中間層容量が十分に大きくない場合、電界はボードの比較的大きな領域に分布し、層間インピーダンスが減少し、戻り電流が上層に戻ることができます。この場合、この信号によって生成されたフィールドは、近くの変化する層信号のフィールドに干渉する可能性があります。これは私たちが望んでいたものではありません。残念ながら、0.062インチの4層ボードでは、層は遠く離れており、層間容量は小さいです

配線がレイヤー1からレイヤー4、またはその逆に変化すると、この問題が写真として表示される場合に、この問題をリードします

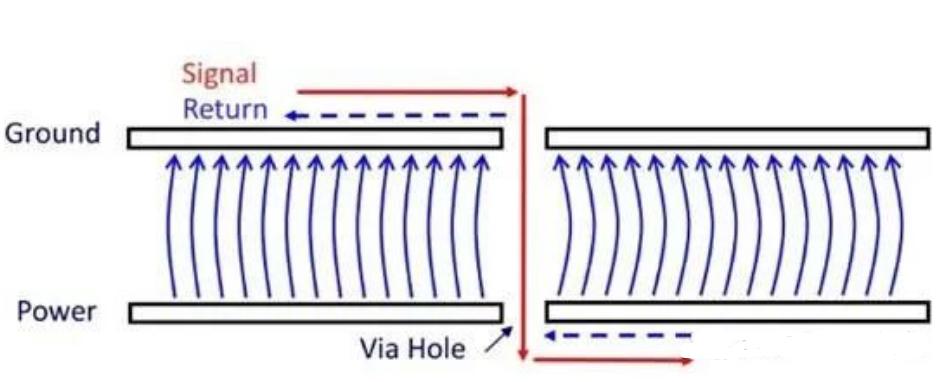

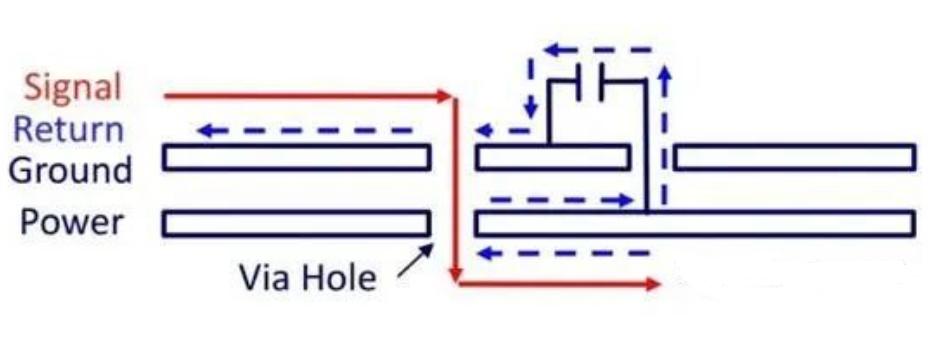

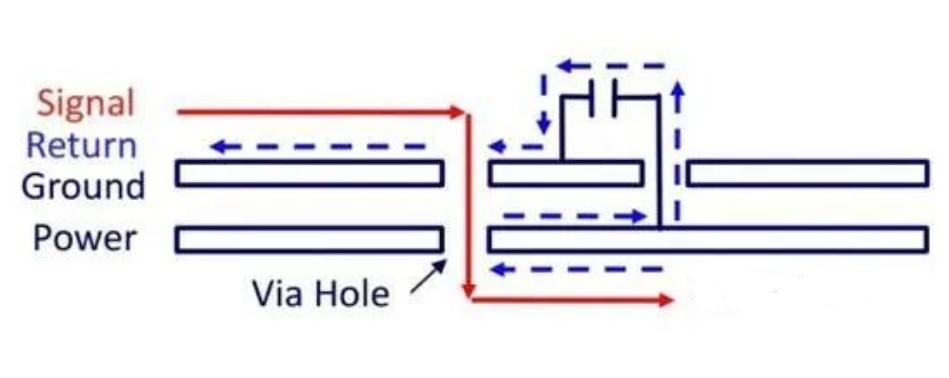

図は、信号がレイヤー1からレイヤー4(赤い線)に追跡すると、戻り電流も変化する必要があることを示しています。信号の周波数が十分に高く、平面が互いに近くにある場合、接地層と電力層の間に存在する層間容量を通るリターン電流が流れる可能性があります。ただし、リターン電流の直接的な導電性接続がないため、戻りパスは中断され、この中断は下の写真として示されている平面間のインピーダンスと考えることができます。

中間層容量が十分に大きくない場合、電界はボードの比較的大きな領域に分布し、層間インピーダンスが減少し、戻り電流が上層に戻ることができます。この場合、この信号によって生成されたフィールドは、近くの変化する層信号のフィールドに干渉する可能性があります。これは私たちが望んでいたものではありません。残念ながら、0.062インチの4層ボードでは、層が遠く離れており(少なくとも0.020インチ)、層間容量は小さいです。その結果、上記の電界干渉が発生します。これは信号の整合性の問題を引き起こすことはないかもしれませんが、確かにより多くのEMIを作成します。これが、カスケードを使用する場合、特にクロックなどの高周波信号に対して、レイヤーを変更することを避ける理由です。

下の写真として示されているリターン電流によって経験されるインピーダンスを減らすために、遷移パス穴の近くにデカップリングコンデンサを追加することは一般的な慣行です。ただし、このデカップリングコンデンサは、自尊心の周波数が低いため、VHF信号には効果がありません。 200〜300 MHzを超える周波数を持つAC信号の場合、コンデンサの分離に頼って低インピーダンスリターンパスを作成することはできません。したがって、デカップリングコンデンサ(200〜300 MHz未満)と、より高い周波数のために比較的大きなインターボードコンデンサが必要です。

この問題は、キー信号の層を変更しないことで回避できます。ただし、4層ボードの小さなボード容量は、別の深刻な問題であるパワートランスミッションにつながります。通常、クロックデジタルICSには大きな一時的な電源電流が必要です。 IC出力の上昇/上下時間が減少するにつれて、より高いレートでエネルギーを供給する必要があります。電荷ソースを提供するために、通常、各ロジックICに非常に近いデカップリングコンデンサを配置します。ただし、問題があります。自尊心の周波数を超えて行くと、デカップリングコンデンサはエネルギーを効率的に保存および伝達することはできません。これらの周波数では、コンデンサがインダクタのように作用するためです。

今日のほとんどのICは急速に上昇/落下時間(約500 PS)にあるため、デカップリングコンデンサのそれよりも高い自己共感周波数を持つ追加のデカップリング構造が必要です。回路基板の層間容量は、十分な静電容量を提供するために層が互いに十分に近い場合、効果的なデカップリング構造になる可能性があります。したがって、一般的に使用されるデカップリングコンデンサに加えて、デジタルICSに一時的な電力を提供するために、密接な間隔の電力層と接地層を使用することを好みます。

共通回路基板の製造プロセスにより、通常、4層ボードの2番目と3番目の層の間に薄い絶縁体がないことに注意してください。 2番目と3番目の層の間に薄い絶縁体を備えた4層ボードは、従来の4層ボードよりもはるかに費用がかかります。