Bei der Layoutdesign der PCB ist das Layout der Komponenten von entscheidender Bedeutung, das den ordentlichen und schönen Grad der Platine sowie die Länge und Menge des gedruckten Drahtes bestimmt und einen gewissen Einfluss auf die Zuverlässigkeit der gesamten Maschine hat.

Eine gute Leiterplatte, zusätzlich zur Realisierung des Prinzips der Funktion, aber auch EMI, EMC, ESD (elektrostatische Entladung), Signalintegrität und andere elektrische Merkmale, aber auch die mechanische Struktur, die Dissipationsprobleme mit großem Power -Chip -Wärme in Betracht ziehen.

Allgemeine Anforderungen an die Layoutspezifikation der PCB -Layout

1, lesen Sie das Entwurfsbeschreibungsdokument, erfüllen Sie die Sonderstruktur, die Sondermodul und andere Layoutanforderungen.

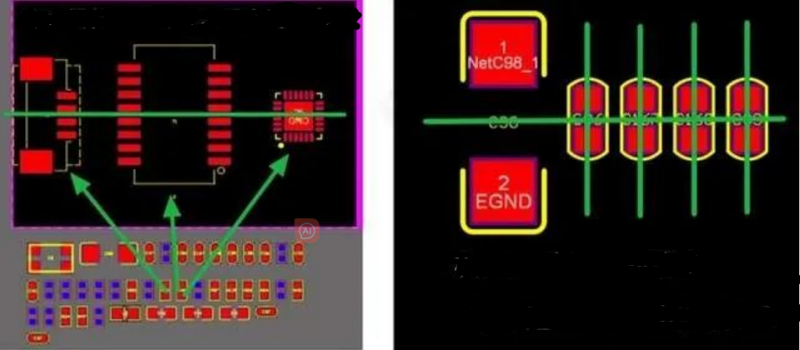

2, setzen Sie den Layout -Gitterpunkt auf 25 Mio., kann durch den Gitterpunkt ausgerichtet werden, der gleiche Abstand; Der Ausrichtungsmodus ist groß, bevor kleine (große Geräte und große Geräte zuerst ausgerichtet sind), und der Ausrichtungsmodus ist in der Mitte, wie in der folgenden Abbildung gezeigt

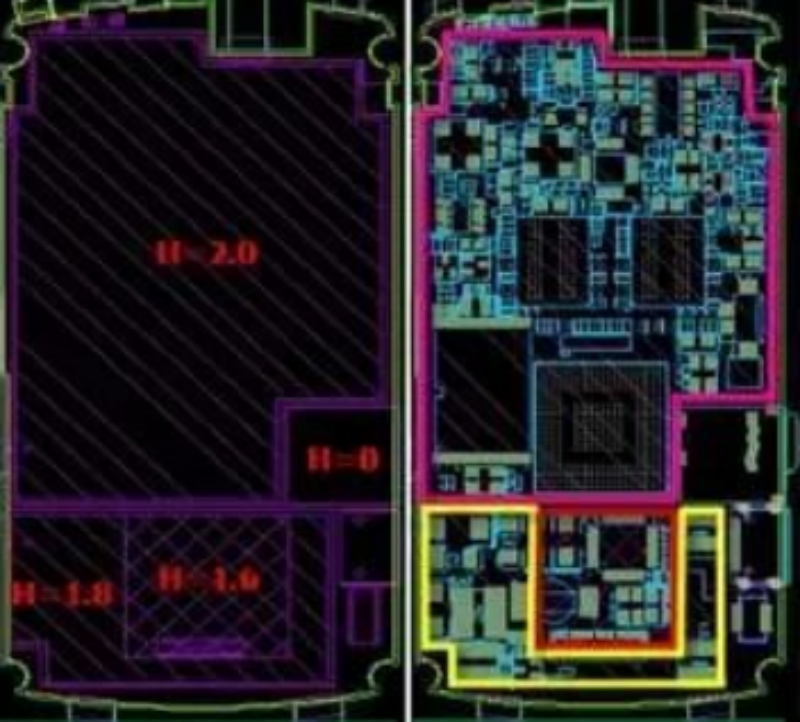

3, erfüllen Sie die verbotene Höhe der verbotenen Flächengrenze, Struktur und spezielle Geräteanforderungen.

① Abbildung 1 (links) unten: Höhengrenze, die deutlich in der mechanischen Schicht oder der Markierungsschicht gekennzeichnet sind, bequem für einen späteren Kreuz-Check;

(2) Stellen Sie vor dem Layout den verbotenen Bereich ein und müssen das Gerät 5 mm vom Rand der Platine entfernt sein, und layern Sie das Gerät nicht, es sei denn, spezielle Anforderungen oder anschließende Platinendesign können eine Prozessanlage hinzufügen.

③ Das Layout der Struktur und der speziellen Geräte kann durch Koordinaten oder durch die Koordinaten des äußeren Rahmens oder der Mittellinie der Komponenten genau positioniert werden.

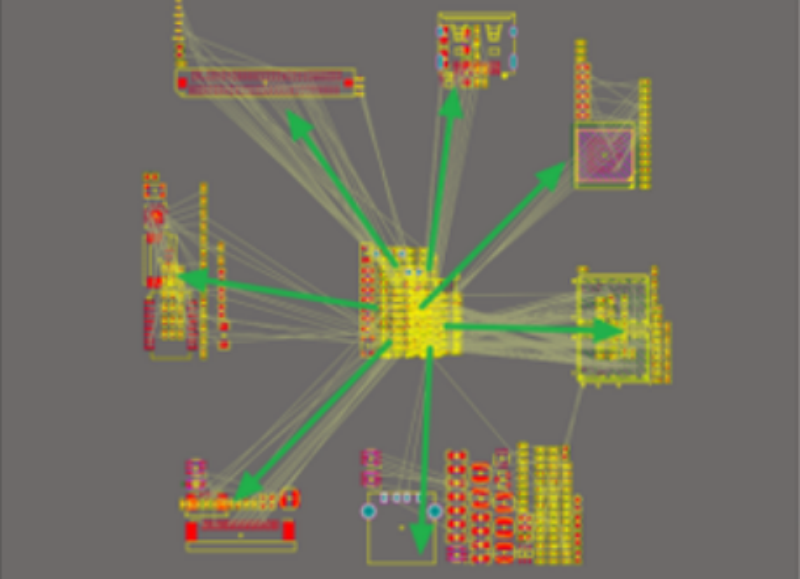

4, das Layout sollte zuerst eine Vor-Layout haben, das Layout nicht direkt starten lassen. Der Vor-Layout kann auf dem Modul-Grab in der PCB-Platine basieren, um die Leitungssignalflussanalyse zu zeichnen und dann auf der Signalflussanalyse in der PCB-Platine der Modul-Auxiliar-Linie zu zeichnen, die negative Position des Moduls in der PCB und der Größe der Besatzungsraumie zu zeichnen. Zeichnen Sie die Hilfslinienbreite 40mil und bewerten Sie die Rationalität des Layouts zwischen Modulen und Modulen durch die obigen Operationen, wie in der folgenden Abbildung gezeigt.

5, das Layout muss den Kanal berücksichtigen, der die Stromleitung verlässt, sollte nicht zu eng zu dicht sein, indem er herausstellt

6, thermische Komponenten (wie Elektrolytkondensatoren, Kristalloszillatoren) sollten so weit wie möglich in der oberen Entlüftung so weit wie möglich von der Stromversorgung und anderen hohen Wärmegeräten entfernt sein

7, um die sensible Moduldifferenzierung, den gesamten Board -Layout -Saldo, die gesamte Board -Kabelkanalreservierung zu erfüllen

Die Hochspannungs- und Hochstromsignale sind vollständig von den schwachen Signalen von kleinen Strömen und niedrigen Spannungen getrennt. Die Hochspannungsteile werden in allen Schichten ohne zusätzliches Kupfer ausgehöhlt. Der Kriechenteil zwischen den Hochspannungsteilen wird gemäß der Standardtabelle überprüft

Das analoge Signal ist mit einer Teilungsbreite von mindestens 20 Mio. vom digitalen Signal getrennt, und das Analogon und RF sind in einer '-' Schriftart oder 'L' -Form gemäß den Anforderungen des modularen Designs angeordnet

Das Hochfrequenzsignal ist vom Niederfrequenzsignal getrennt, der Trennabstand beträgt mindestens 3 mm und das Kreuzlayout kann nicht sichergestellt werden

Das Layout von wichtigen Signalgeräten wie Kristalloszillator und Taktentreiber sollte weit vom Grenzflächenschaltungslayout entfernt sein, nicht am Rand der Platine und mindestens 10 mm vom Rand der Platine entfernt. Der Kristall- und Kristalloszillator sollte in der Nähe des Chips platziert werden, in derselben Schicht gelegt, keine Löcher schlagen und Raum für den Boden reservieren

Die gleiche Strukturschaltung übernimmt das "symmetrische" Standardlayout (direkte Wiederverwendung desselben Moduls), um die Konsistenz des Signals zu erfüllen

Nach dem Design der PCB müssen wir Analysen und Inspektionen durchführen, um die Produktion reibungsloser zu machen.