Der Via ist eine der wichtigsten Komponenten der mehrschichtigen PCB, und die Bohrkosten machen normalerweise 30% bis 40% der Kosten der PCB-Platine aus. Einfach ausgedrückt, jedes Loch auf der PCB kann als via bezeichnet werden.

Das grundlegende Konzept der via:

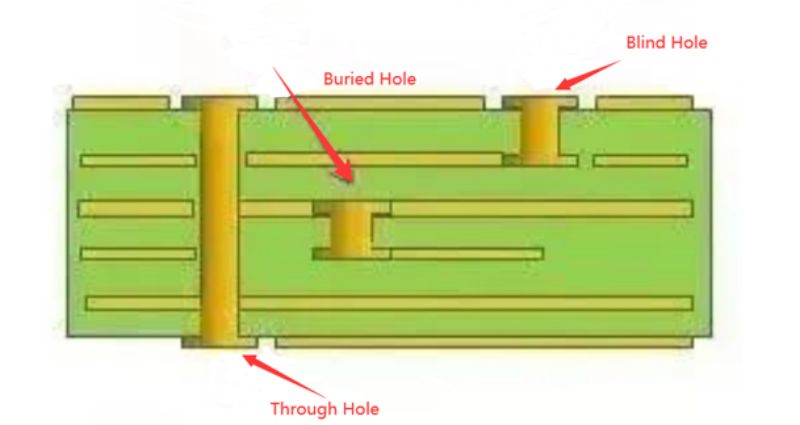

Aus der Sicht der Funktion kann der Via in zwei Kategorien unterteilt werden: Eine wird als elektrische Verbindung zwischen den Schichten verwendet und der andere wird als Befestigung oder Positionierung des Geräts verwendet. Wenn aus dem Prozess, sind diese Löcher im Allgemeinen in drei Kategorien unterteilt, nämlich blinde Löcher, vergrabene Löcher und durch Löcher.

Blinde Löcher befinden sich auf den oberen und unteren Oberflächen der gedruckten Leiterplatte und haben eine bestimmte Tiefe für die Verbindung des Oberflächenkreises und der inneren Schaltung unten, und die Tiefe der Löcher überschreitet normalerweise kein bestimmtes Verhältnis (Apertur).

Das vergrabene Loch bezieht sich auf das Verbindungsloch in der inneren Schicht der gedruckten Leiterplatte, die sich nicht an die Oberfläche der Platine erstreckt. Die beiden oben genannten Arten von Löchern befinden sich in der inneren Schicht der Leiterplatte, die durch den Durchgangsleistungsprozess vor der Laminierung abgeschlossen wird, und mehrere innere Schichten können während der Bildung des durch Lochs überlappt werden.

Der dritte Typ wird durch Löcher bezeichnet, die durch die gesamte Leiterplatte gelangen und zur Erzielung einer internen Zusammenfassung oder als Installationspositionierungslöcher für Komponenten verwendet werden können. Da das Durchlebnis leichter zu erreichen ist und die Kosten niedriger sind, verwendet die überwiegende Mehrheit der gedruckten Leiterplatten sie eher als die anderen beiden durch Löcher. Die folgenden Löcher ohne besondere Anweisungen werden als durch Löcher angesehen.

Aus Sicht der Konstruktion besteht ein Via hauptsächlich aus zwei Teilen, einer ist die Mitte des Bohrlochs und der andere ist der Schweißbadbereich um das Bohrloch. Die Größe dieser beiden Teile bestimmt die Größe von via.

Offensichtlich wollen die Designer im Hochgeschwindigkeits-PCB-Design mit hoher Dichte immer so klein wie möglich, so dass mehr Kabelraum übrig bleiben kann.

Die Reduzierung der Übergröße bringt jedoch auch zu einer Erhöhung der Kosten, und die Größe des Lochs kann nicht auf unbestimmte Zeit reduziert werden. Es wird durch Bohr- und Elektroplattentechnologie begrenzt: Je kleiner das Loch ist, desto länger dauert es, dass die Bohrung von der Mitte leichter abweichen wird. Wenn die Tiefe des Lochs mehr als das 6 -fache des Durchmessers des Lochs beträgt, ist es unmöglich sicherzustellen, dass die Lochwand gleichmäßig mit Kupfer plattiert werden kann.

Wenn beispielsweise die Dicke (durch Lochtiefe) einer normalen 6-Schicht-PCB-Platine 50 Mio. beträgt, kann der minimale Bohrdurchmesser, den PCB-Hersteller unter normalen Bedingungen bereitstellen können, nur 8 Mio. erreichen. Mit der Entwicklung der Laserbohrtechnologie kann die Größe des Bohrers auch immer kleiner und kleiner sein, und der Durchmesser des Lochs ist im Allgemeinen weniger als oder gleich 6 MILs, wir werden als Mikroholes bezeichnet.

Mikrolöcher werden häufig in der HDI -Konstruktion (Hochdichte -Interconnect -Struktur) verwendet, und die Mikrolochtechnologie kann es ermöglichen, das Loch direkt auf das Pad zu bohren, was die Leistungsleistung erheblich verbessert und den Kabelraum spart. Der Via erscheint als Breakpoint der Impedanzdiskontinuität auf der Übertragungsleitung, was zu einem Spiegelbild des Signals führt. Im Allgemeinen ist die äquivalente Impedanz des Lochs etwa 12% niedriger als die Übertragungsleitung, beispielsweise wird die Impedanz einer Übertragungsleitung von 50 Ohm um 6 Ohm reduziert, wenn es durch das Loch verläuft (speziell und die Größe der VIA, auch die Plattendicke, nicht eine absolute Reduzierung).

Die Reflexion, die durch die Impedanzdiskontinuität über über die Überlastung verursacht wird, ist jedoch tatsächlich sehr gering und ihr Reflexionskoeffizient beträgt nur:

(44-50)/(44 + 50) = 0,06

Die Probleme, die sich aus dem über die Via ergeben, konzentrieren sich stärker auf die Auswirkungen von parasitärer Kapazität und Induktivität.

Parasitäre Kapazität und Induktivität von Via

Es gibt eine parasitäre Streunerkapazität in sich selbst. Wenn der Durchmesser der Lötwiderstandszone auf der verlegten Schicht D2 ist, ist der Durchmesser des Lötkissens D1, die Dicke der PCB -Platine t und die Dielektrizitätskonstante des Substrats ist ε, die parasitäre Kapazität des Durchslochs ist ungefähr:

C = 1,41εtd1/(d2-d1)

Der Haupteffekt der parasitären Kapazität auf den Stromkreis besteht darin, die Anstiegszeit des Signals zu verlängern und die Geschwindigkeit der Schaltung zu verringern.

Zum Beispiel für eine Leiterplatte mit einer Dicke von 50 Mio., wenn der Durchmesser des Via Pad 20mil (der Durchmesser des Bohrlochs 10 Mio. beträgt) und der Durchmesser der Lötbeständigkeitszone 40 MIL beträgt, können wir die parasitäre Kapazität der oberen Formula angenähern:

C = 1,41 x 4,4x0.050x0.020/(0,040-0.020) = 0,31PF

Die durch diesen Teil der Kapazität verursachte Anstiegszeitveränderung beträgt ungefähr:

T10-90 = 2,2C (Z0/2) = 2,2 x 0,31X (50/2) = 17,05 Ps

Aus diesen Werten ist ersichtlich, dass zwar die Nützlichkeit der Anstiegsverzögerung, die durch die parasitäre Kapazität eines einzelnen Via verursacht wird, nicht sehr offensichtlich ist, wenn die via mehrmals in der Linie verwendet wird, um zwischen Schichten zu wechseln, werden mehrere Löcher verwendet, und das Design sollte sorgfältig berücksichtigt werden. Im tatsächlichen Design kann die parasitäre Kapazität verringert werden, indem der Abstand zwischen dem Loch und dem Kupferbereich (Anti-Pad) oder dem Verringern des Durchmessers des Pads erhöht wird.

Bei der Gestaltung digitaler Hochgeschwindigkeitsschaltungen ist der durch die parasitäre Induktivität verursachte Schaden häufig größer als der Einfluss der parasitären Kapazität. Seine parasitäre Serie -Induktivität wird den Beitrag des Bypass -Kondensators schwächen und die Filterwirksamkeit des gesamten Leistungssystems schwächen.

Wir können die folgende empirische Formel verwenden, um einfach die parasitäre Induktivität einer Durchläuf-Annäherung zu berechnen:

L = 5,08H [ln (4H/d) +1]

Wo L auf die Induktivität von via bezieht, ist H die Länge von via und D ist der Durchmesser des zentralen Lochs. Aus der Formel ist ersichtlich, dass der Durchmesser des via wenig Einfluss auf die Induktivität hat, während die Länge des VIC den größten Einfluss auf die Induktivität hat. Mit dem obigen Beispiel kann die Außenloch-Induktivität berechnet werden als:

L = 5.08x0.050 [LN (4x0.050/0,010) +1] = 1.015nh

Wenn die Anstiegszeit des Signals 1 ns beträgt, beträgt seine äquivalente Impedanzgröße:

Xl = πl/t10-90 = 3,19 Ω

Eine solche Impedanz kann nicht in Gegenwart von Hochfrequenzstrom durch insbesondere durch den Bypass-Kondensator ignoriert werden, wenn der Bypass-Kondensator zwei Löcher durchlaufen muss, wenn sie die Leistungsschicht und die Bildung verbinden, so dass die parasitäre Induktivität des Lochs multipliziert wird.

Wie benutze ich das Via?

Durch die obige Analyse der parasitären Eigenschaften des Lochs können wir sehen, dass scheinbar einfache Löcher in Hochgeschwindigkeits-PCB-Design häufig große negative Auswirkungen auf die Gestaltung der Schaltung haben. Um die durch die parasitären Wirkung des Lochs verursachten nachteiligen Auswirkungen zu verringern, kann das Design so weit wie möglich sein:

Wählen Sie aus den beiden Aspekten der Kosten und der Signalqualität eine angemessene Größe der Übergröße. Bei Bedarf können Sie in Betracht ziehen, verschiedene Größen von VIAS zu verwenden, z. B. für die Stromversorgung oder die Erdungslöcher. Sie können in Betracht ziehen, eine größere Größe zu verwenden, um die Impedanz zu verringern, und für die Signalverdrahtung können Sie eine kleinere via verwenden. Natürlich erhöhen sich die entsprechenden Kosten, wenn die Größe der Via -abnimmt, auch die entsprechenden Kosten

Die beiden oben diskutierten Formeln können zu dem Schluss gezogen werden, dass die Verwendung einer dünneren PCB

Die Signalverkabelung auf der PCB -Platine sollte nicht so weit wie möglich geändert werden, dh versuchen, keine unnötige VIAS zu verwenden.

Die Vias müssen in die Stifte der Stromversorgung und des Bodens gebohrt werden. Je kürzer die Führung zwischen den Stiften und den Vias ist, desto besser. Mehrere Löcher können parallel gebohrt werden, um die äquivalente Induktivität zu verringern.

Stellen Sie einige geerdete Durchlöcher in der Nähe der Durchlöcher der Signaländerung, um die nächste Schleife für das Signal bereitzustellen. Sie können sogar einige überschüssige Bodenlöcher auf das Leiterplatten platzieren.

Für Hochgeschwindigkeits-PCB-Boards mit hoher Dichte können Sie in Betracht ziehen, Mikroleiten zu verwenden.