1. Việc hình thành các khe trong quá trình thiết kế PCB bao gồm:

Độ cao gây ra bởi sự phân chia điện hoặc máy bay mặt đất; Khi có nhiều nguồn cung cấp năng lượng hoặc căn cứ khác nhau trên PCB, thường không thể phân bổ một mặt phẳng hoàn chỉnh cho mỗi mạng cung cấp điện và mạng lưới mặt đất. Cách tiếp cận phổ biến là hoặc thực hiện phân chia điện hoặc phân chia mặt đất trên nhiều máy bay. Các khe được hình thành giữa các bộ phận khác nhau trên cùng một mặt phẳng.

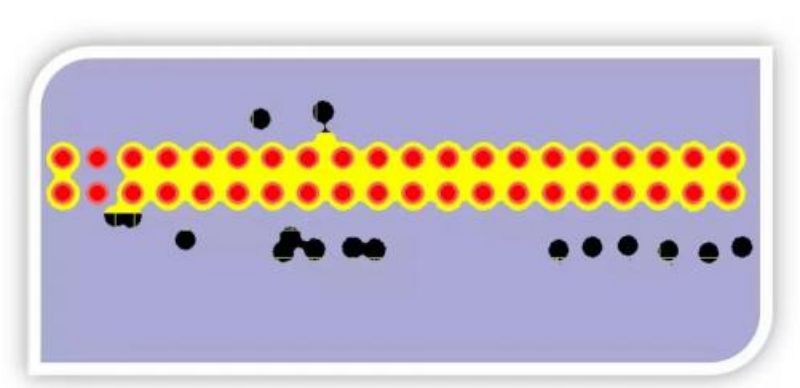

Các lỗ qua quá dày đặc để tạo thành các khe (thông qua các lỗ bao gồm miếng đệm và vias); Khi các lỗ qua đi qua lớp mặt đất hoặc lớp năng lượng mà không có kết nối điện với chúng, một số không gian cần được để xung quanh các lỗ thông qua để cách ly điện; Nhưng khi các lỗ thông qua khi các lỗ quá gần nhau, các vòng đệm trùng nhau, các khe tạo ra.

2. Tác động của việc đánh dấu vào hiệu suất EMC của phiên bản PCB

Grooving sẽ có tác động nhất định đến hiệu suất EMC của bảng PCB. Tác động này có thể là tiêu cực hoặc tích cực. Đầu tiên chúng ta cần hiểu sự phân bố dòng chảy bề mặt của tín hiệu tốc độ cao và tín hiệu tốc độ thấp. Ở tốc độ thấp, dòng chảy dọc theo đường dẫn điện trở thấp nhất. Hình dưới đây cho thấy làm thế nào khi một dòng điện tốc độ thấp chảy từ A đến B, tín hiệu trả về của nó trở lại từ mặt phẳng mặt đất đến nguồn. Tại thời điểm này, phân phối dòng chảy bề mặt rộng hơn.

Ở tốc độ cao, ảnh hưởng của độ tự cảm lên đường dẫn trả về tín hiệu sẽ vượt quá ảnh hưởng của điện trở. Tín hiệu trở lại tốc độ cao sẽ chảy dọc theo đường dẫn trở kháng thấp nhất. Tại thời điểm này, phân phối dòng bề mặt rất hẹp và tín hiệu trả về được cô đặc dưới đường tín hiệu trong một gói.

Khi có các mạch không tương thích trên PCB, cần có quá trình xử lý phân tách mặt đất, đó là, các mặt phẳng mặt đất được đặt riêng theo các điện áp cung cấp điện khác nhau, tín hiệu kỹ thuật số và tương tự, tín hiệu tốc độ cao và tốc độ thấp, và tín hiệu dòng điện cao và dòng điện thấp. Từ việc phân phối tín hiệu tốc độ cao và lợi nhuận tín hiệu tốc độ thấp được đưa ra ở trên, có thể dễ dàng hiểu rằng nối đất riêng biệt có thể ngăn chặn sự chồng chất của tín hiệu trở lại từ các mạch không tương thích và ngăn chặn sự kết hợp trở kháng đường nối đất chung.

Nhưng bất kể tín hiệu tốc độ cao hoặc tín hiệu tốc độ thấp, khi các đường tín hiệu vượt qua các khe trên mặt phẳng điện hoặc mặt phẳng mặt đất, sẽ xảy ra nhiều vấn đề nghiêm trọng, bao gồm:

Tăng diện tích vòng lặp hiện tại làm tăng độ tự cảm của vòng lặp, làm cho dạng sóng đầu ra dễ dao động;

Đối với các đường tín hiệu tốc độ cao yêu cầu điều khiển trở kháng nghiêm ngặt và được định tuyến theo mô hình dòng chảy, mô hình dòng chảy sẽ bị phá hủy do độ dốc của mặt phẳng trên hoặc mặt phẳng dưới hoặc mặt phẳng trên và dưới, dẫn đến sự gián đoạn trở kháng và toàn vẹn tín hiệu nghiêm trọng. vấn đề tình dục;

Tăng phát xạ bức xạ vào không gian và dễ bị nhiễu từ từ trường không gian;

Điện áp tần số cao trên độ tự cảm vòng lặp tạo thành một nguồn bức xạ chế độ chung và bức xạ chế độ chung được tạo ra thông qua các dây cáp bên ngoài;

Tăng khả năng nhiễu xuyên âm tín hiệu tần số cao với các mạch khác trên bảng.

Khi có các mạch không tương thích trên PCB, cần có quá trình xử lý phân tách mặt đất, đó là, các mặt phẳng mặt đất được đặt riêng theo các điện áp cung cấp điện khác nhau, tín hiệu kỹ thuật số và tương tự, tín hiệu tốc độ cao và tốc độ thấp, và tín hiệu dòng điện cao và dòng điện thấp. Từ việc phân phối tín hiệu tốc độ cao và lợi nhuận tín hiệu tốc độ thấp được đưa ra ở trên, có thể dễ dàng hiểu rằng nối đất riêng biệt có thể ngăn chặn sự chồng chất của tín hiệu trở lại từ các mạch không tương thích và ngăn chặn sự kết hợp trở kháng đường nối đất chung.

Nhưng bất kể tín hiệu tốc độ cao hoặc tín hiệu tốc độ thấp, khi các đường tín hiệu vượt qua các khe trên mặt phẳng điện hoặc mặt phẳng mặt đất, sẽ xảy ra nhiều vấn đề nghiêm trọng, bao gồm:

Tăng diện tích vòng lặp hiện tại làm tăng độ tự cảm của vòng lặp, làm cho dạng sóng đầu ra dễ dao động;

Đối với các đường tín hiệu tốc độ cao yêu cầu điều khiển trở kháng nghiêm ngặt và được định tuyến theo mô hình dòng chảy, mô hình dòng chảy sẽ bị phá hủy do độ dốc của mặt phẳng trên hoặc mặt phẳng dưới hoặc mặt phẳng trên và dưới, dẫn đến sự gián đoạn trở kháng và toàn vẹn tín hiệu nghiêm trọng. vấn đề tình dục;

Tăng phát xạ bức xạ vào không gian và dễ bị nhiễu từ từ trường không gian;

Điện áp tần số cao trên độ tự cảm vòng lặp tạo thành một nguồn bức xạ chế độ chung và bức xạ chế độ chung được tạo ra thông qua các dây cáp bên ngoài;

Tăng khả năng nhiễu xuyên âm tín hiệu tần số cao với các mạch khác trên bảng

3. Phương pháp thiết kế PCB để đánh rã

Việc xử lý các rãnh nên tuân theo các nguyên tắc sau:

Đối với các đường tín hiệu tốc độ cao yêu cầu kiểm soát trở kháng nghiêm ngặt, dấu vết của chúng bị nghiêm cấm không bị phân chia các đường phân chia để tránh gây ra sự gián đoạn trở kháng và gây ra các vấn đề toàn vẹn tín hiệu nghiêm trọng;

Khi có các mạch không tương thích trên PCB, nên thực hiện sự phân tách mặt đất, nhưng sự phân tách mặt đất sẽ không khiến các đường tín hiệu tốc độ cao bị chia cắt chéo, và cố gắng không làm cho các đường tín hiệu tốc độ thấp bị chia cắt chéo;

Khi định tuyến trên các khe là không thể tránh khỏi, nên thực hiện bắc cầu;

Đầu nối (bên ngoài) không nên được đặt trên lớp đất. Nếu có sự khác biệt tiềm năng lớn giữa điểm A và điểm B trên lớp đất trong hình, bức xạ chế độ chung có thể được tạo ra thông qua cáp bên ngoài;

Khi thiết kế PCB cho các đầu nối mật độ cao, trừ khi có các yêu cầu đặc biệt, bạn thường nên đảm bảo rằng mạng nối đất bao quanh mỗi pin. Bạn cũng có thể sắp xếp mạng lưới mặt đất đồng đều khi sắp xếp các chân để đảm bảo tính liên tục của mặt phẳng mặt đất và ngăn chặn việc sản xuất khe hở