VIA là một trong những thành phần quan trọng của PCB nhiều lớp và chi phí khoan thường chiếm 30% đến 40% chi phí của bảng PCB. Nói một cách đơn giản, mọi lỗ trên PCB có thể được gọi là VIA.

Khái niệm cơ bản của VIA:

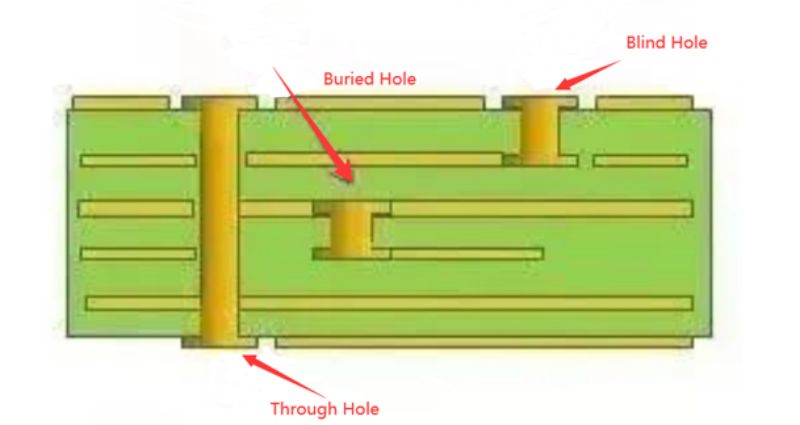

Từ quan điểm của chức năng, VIA có thể được chia thành hai loại: một loại được sử dụng làm kết nối điện giữa các lớp và phần kia được sử dụng như một bản sửa lỗi hoặc định vị của thiết bị. Nếu từ quá trình, những lỗ hổng này thường được chia thành ba loại, cụ thể là các lỗ mù, các lỗ bị chôn vùi và qua các lỗ.

Các lỗ mù được đặt trên bề mặt trên và dưới của bảng mạch in và có độ sâu nhất định cho sự kết nối của mạch bề mặt và mạch bên trong bên dưới, và độ sâu của các lỗ thường không vượt quá tỷ lệ nhất định (khẩu độ).

Lỗ bị chôn vùi đề cập đến lỗ kết nối nằm trong lớp bên trong của bảng mạch in, không mở rộng lên bề mặt của bảng. Hai loại lỗ trên được đặt trong lớp bên trong của bảng mạch, được hoàn thành bởi quá trình đúc qua lỗ trước khi dán, và một số lớp bên trong có thể được chồng lên nhau trong quá trình hình thành lỗ thông qua.

Loại thứ ba được gọi là các lỗ thông qua, đi qua toàn bộ bảng mạch và có thể được sử dụng để đạt được kết nối bên trong hoặc làm lỗ định vị cài đặt cho các thành phần. Bởi vì lỗ thông qua dễ dàng đạt được trong quá trình và chi phí thấp hơn, phần lớn các bảng mạch in sử dụng nó, thay vì hai cái còn lại thông qua các lỗ. Các lỗ sau đây, không có hướng dẫn đặc biệt, được coi là thông qua các lỗ.

Từ quan điểm thiết kế, A VIA chủ yếu bao gồm hai phần, một phần là giữa lỗ khoan, và phần còn lại là khu vực hàn xung quanh lỗ khoan. Kích thước của hai phần này xác định kích thước của VIA.

Rõ ràng, trong thiết kế PCB có mật độ cao, tốc độ cao, các nhà thiết kế luôn muốn lỗ nhỏ nhất có thể, do đó, nhiều không gian hệ thống dây có thể được để lại nhỏ hơn, điện dung ký sinh của chính nó nhỏ hơn, dễ dàng hơn cho các mạch tốc độ cao.

Tuy nhiên, việc giảm kích thước thông qua cũng mang lại sự gia tăng chi phí và kích thước của lỗ không thể giảm vô thời hạn, nó bị giới hạn bởi công nghệ khoan và mạ điện: lỗ càng nhỏ, việc khoan càng dài, càng dễ đi chệch khỏi trung tâm; Khi độ sâu của lỗ gấp hơn 6 lần đường kính của lỗ, không thể đảm bảo rằng thành lỗ có thể được mạ đồng đều bằng đồng.

Ví dụ, nếu độ dày (qua độ sâu lỗ) của bảng PCB 6 lớp bình thường là 50mil, thì đường kính khoan tối thiểu mà các nhà sản xuất PCB có thể cung cấp trong điều kiện bình thường chỉ có thể đạt tới 8mil. Với sự phát triển của công nghệ khoan laser, kích thước của việc khoan cũng có thể nhỏ hơn và nhỏ hơn, và đường kính của lỗ thường nhỏ hơn hoặc bằng 6 triệu, chúng ta được gọi là vi mạch.

Các vi sinh vật thường được sử dụng trong thiết kế HDI (cấu trúc kết nối mật độ cao) và công nghệ siêu nhỏ có thể cho phép lỗ được khoan trực tiếp trên miếng đệm, giúp cải thiện đáng kể hiệu suất mạch và tiết kiệm không gian nối dây. VIA xuất hiện như một điểm dừng của sự gián đoạn trở kháng trên đường truyền, gây ra sự phản xạ của tín hiệu. Nói chung, trở kháng tương đương của lỗ thấp hơn khoảng 12% so với đường truyền, ví dụ, trở kháng của đường truyền 50 ohms sẽ giảm 6 ohms khi nó đi qua lỗ (cụ thể và kích thước của VIA, độ dày của tấm cũng liên quan, không phải là giảm tuyệt đối).

Tuy nhiên, sự phản ánh gây ra bởi sự gián đoạn trở kháng thông qua thực sự rất nhỏ và hệ số phản xạ của nó chỉ là:

(44-50)/(44 + 50) = 0,06

Các vấn đề phát sinh từ VIA tập trung hơn vào tác động của điện dung ký sinh và độ tự cảm.

Via điện dung ký sinh và độ tự cảm

Có một điện dung đi lạc ký sinh trong chính Via. Nếu đường kính của vùng điện trở hàn trên lớp đặt là D2, đường kính của miếng hàn là D1, độ dày của bảng PCB là T và hằng số điện môi của chất nền là ε, điện dung ký sinh của lỗ thông qua:

C = 1.41 extd1/(D2-D1)

Tác động chính của điện dung ký sinh trên mạch là kéo dài thời gian tăng của tín hiệu và giảm tốc độ của mạch.

Ví dụ, đối với PCB có độ dày 50mil, nếu đường kính của PAD VIA là 20mil (đường kính của lỗ khoan là 10 triệu) và đường kính của vùng điện trở hàn là 40mil, thì chúng ta có thể xấp xỉ điện dung ký sinh của Via By By By

C = 1.41x4.4x0.050x0.020/(0,040-0.020) = 0,31pf

Lượng thay đổi thời gian tăng gây ra bởi phần này của điện dung là gần như:

T10-90 = 2.2C (Z0/2) = 2.2x0.31x (50/2) = 17.05ps

Có thể thấy từ các giá trị này rằng mặc dù tiện ích của độ trễ tăng gây ra bởi điện dung ký sinh của một VIA là không rõ ràng, nếu VIA được sử dụng nhiều lần trong dòng để chuyển đổi giữa các lớp, nhiều lỗ sẽ được sử dụng và thiết kế nên được xem xét cẩn thận. Trong thiết kế thực tế, điện dung ký sinh có thể giảm bằng cách tăng khoảng cách giữa lỗ và diện tích đồng (chống PAD) hoặc giảm đường kính của pad.

Trong thiết kế các mạch kỹ thuật số tốc độ cao, tác hại gây ra bởi độ tự cảm ký sinh thường lớn hơn ảnh hưởng của điện dung ký sinh. Độ tự cảm loạt ký sinh của nó sẽ làm suy yếu sự đóng góp của tụ điện Bypass và làm suy yếu hiệu quả lọc của toàn bộ hệ thống điện.

Chúng ta có thể sử dụng công thức thực nghiệm sau đây để đơn giản tính toán độ tự cảm ký sinh của một xấp xỉ qua lỗ thông qua:

L = 5.08h [LN (4H/D) +1]]

Trong đó L đề cập đến độ tự cảm của VIA, H là chiều dài của VIA và D là đường kính của lỗ trung tâm. Có thể thấy từ công thức rằng đường kính của VIA có ít ảnh hưởng đến độ tự cảm, trong khi độ dài của VIA có ảnh hưởng lớn nhất đến độ tự cảm. Vẫn sử dụng ví dụ trên, độ tự cảm ngoài lỗ có thể được tính toán là:

L = 5.08x0.050 [LN (4x0.050/0,010) +1] = 1.015NH

Nếu thời gian tăng của tín hiệu là 1NS, thì kích thước trở kháng tương đương của nó là:

Xl = πl/t10-90 = 3.19Ω

Trở kháng như vậy không thể bị bỏ qua với sự hiện diện của dòng tần số cao thông qua, đặc biệt, lưu ý rằng tụ điện bỏ qua cần phải đi qua hai lỗ khi kết nối lớp công suất và sự hình thành, do đó độ tự cảm ký sinh của lỗ sẽ được nhân lên.

Làm thế nào để sử dụng VIA?

Thông qua phân tích trên về các đặc điểm ký sinh của lỗ, chúng ta có thể thấy rằng trong thiết kế PCB tốc độ cao, các lỗ dường như đơn giản thường mang lại những tác động tiêu cực lớn cho thiết kế của mạch. Để giảm các tác động bất lợi gây ra bởi hiệu ứng ký sinh của lỗ, thiết kế có thể càng xa càng tốt:

Từ hai khía cạnh của chất lượng chi phí và tín hiệu, chọn một kích thước hợp lý của kích thước thông qua. Nếu cần thiết, bạn có thể xem xét sử dụng các kích thước khác nhau của VIAS, chẳng hạn như để cung cấp điện hoặc lỗ dây mặt đất, bạn có thể xem xét sử dụng kích thước lớn hơn để giảm trở kháng và đối với hệ thống dây tín hiệu, bạn có thể sử dụng thông qua nhỏ hơn. Tất nhiên, khi kích thước của thông qua giảm, chi phí tương ứng cũng sẽ tăng

Hai công thức được thảo luận ở trên có thể được kết luận rằng việc sử dụng bảng PCB mỏng hơn có lợi cho việc giảm hai thông số ký sinh của VIA

Dây dẫn tín hiệu trên bảng PCB không nên được thay đổi càng xa càng tốt, nghĩa là, cố gắng không sử dụng VIAS không cần thiết.

VIAS phải được khoan vào các chân của nguồn điện và mặt đất. Chất dẫn càng ngắn giữa các chân và VIAS thì càng tốt. Nhiều lỗ có thể được khoan song song để giảm độ tự cảm tương đương.

Đặt một số lỗ xuyên qua các lỗ gần các lỗ xuyên qua của sự thay đổi tín hiệu để cung cấp vòng lặp gần nhất cho tín hiệu. Bạn thậm chí có thể đặt một số lỗ hổng mặt đất dư thừa trên bảng PCB.

Đối với các bảng PCB tốc độ cao có mật độ cao, bạn có thể xem xét sử dụng các lỗ nhỏ.