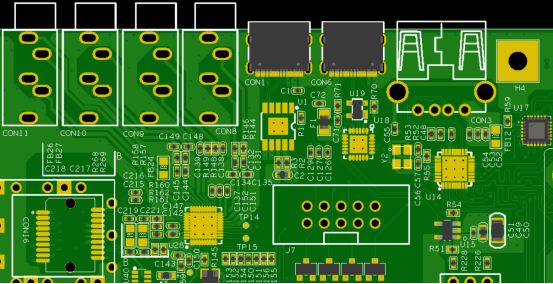

PCB макеты һәм чыбык проблемасына килгәндә, бүген без сираль сафлыгы анализы (си), электромагнити туплау анализы (EMC), электр сафлыгы анализы (PI) турында сөйләшмәячәкбез. Judәм җитештерү (DFM) турында гына сөйләшкәндә, җитештерүнең нигезсез дизайны шулай ук продукт дизайнының уңышсызлыгына китерәчәк.

PCB макетында уңышлы DFM мөһим DFM чикләүләрен исәпкә алып дизайн кагыйдәләре белән башлана. Түбәндә күрсәтелгән DFM кагыйдәләре хәзерге җитештерүчеләр таба алган заманча проект сәләтен чагылдыра. PCB дизайн кагыйдәләре куелган чикләрне бозмагыз, стандарт дизайн чикләүләрен тәэмин итә ала.

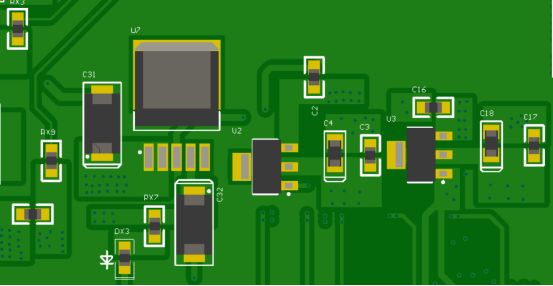

PCB маршрутының DFM проблемасы яхшы PCB макетына бәйле, һәм көйләү кагыйдәләре, үткәрүнең саны, гадәттә кыска юлларны тиз тоташтыр, аннары лабиринт чыбыклары үткәрелә. Глобаль маршрутның оптимизациясе башта чыбыкларда үткәрелә, һәм яңадан чыбык гомуми эффектны һәм DFM җитештерүне яхшыртырга тырышалар.

1.Мин җайланмалар

Deviceайланма казанышлары арасы җыю таләпләренә туры килә, һәм, гадәттә, BGA җайланмалары өчен IT җайланмалары өчен 80милнән 80милнән, гадәттә, 200миг. Productionитештерү процессының сыйфатын һәм уңышы яхшырту өчен, җайланма җыю таләпләренә туры килә ала.

Гадәттә, җайланма кадакларының SMD такталары арасындагы ераклык 6милдән зуррак булырга тиеш, һәм сатылган сатучы бакчының ясалу куәте 4мил. SMD такталар арасындагы ераклык 5милдән ким булса, эретелгән тәрәзәдән ким булса, эретүче күперне саклап булмый, нәтиҗәдә, зур схемага китерәчәк, алар кыска схемага китерәчәк.

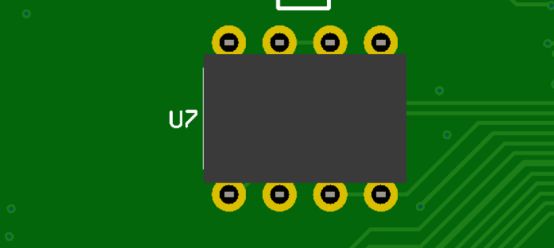

2. Deviceайланма

PIN арасы, дулкыннар эретүче җайланмаларның юнәлеше һәм арасы исәпкә алынырга тиеш. Deviceайланманың PIN арасыу калинына китерәчәк, ул кыска схемага китерәчәк.

Күпчелек дизайнерлар линия җайланмаларын (THTS) куллануны киметә яки аларны такта бер ягында урнаштыралар. Ләкин, линда җайланмалар еш котылгысыз. Комбинацияләнгән очракта, беренче җайланма иң югары катламга урнаштырылса, аскы катламга урнаштырыла, кайбер очракларда ул бер яклы дулкын эретүенә тәэсир итәчәк. Бу очракта, эретеп ябыштыру процесслары, мәсәлән, эретеп ябыштыру, кулланыла.

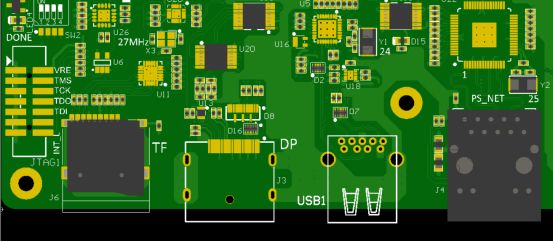

3. Компонентлар һәм тәлинкән кыры арасындагы ераклык

Әгәр дә ул эретеп ябышса, электрон компонентлар белән Директорлар арасындагы ара, гадәттә, төрле үсемлекләр бар.

Ләкин, тәлинкә кыры энберләнгәндә, ул машина тимер юлын очратырга һәм компонентларга зыян китерергә мөмкин. Тәлинкә читендә җайланма җитештерү процессында бетереләчәк. Әгәр дә такта кечкенә булса, эретеп ябыштыру сыйфаты тәэсир итәчәк.

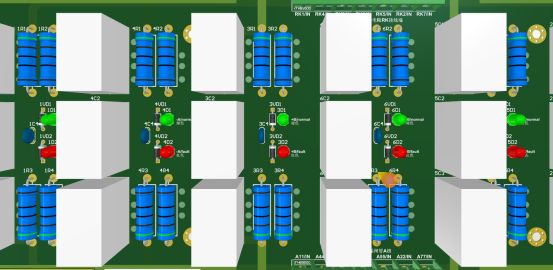

4. Highгары / Түбән җайланмаларның

Электрон компонентлар, төрле формалар, төрле линияләр бар, шуңа күрә басылган советлар җыю ысулында төрле. Яхшы макет машина тотрыклы эшне, шок дәлилне киметергә, зыянны киметергә, шулай ук машинада чиста һәм матур эффект ала ала.

Кечкенә җайланмалар югары җайланмалар тирәсендә билгеле бер ераклыкта сакланырга тиеш. Deviceайланма дистанция җайланмасына дистанция кечкенә, тигез булмаган җылылык дулкыны бар, бу эретеп үскәннән соң ярлы эретеп ябышырга мөмкин.

5. Deviceайланма җайланмасы

Гомумән СМТ эшкәртүдә машина Монтажтагы кайбер хаталарны исәпкә алырга, хезмәт күрсәтү һәм визуаль тикшерү уңайлыгын исәпкә алырга кирәк. Ике күрше компонентлар бик якын булырга һәм билгеле бер куркынычсыз ераклыкта калырга тиеш түгел.

Кисәк компонентлары, согы, соци һәм ялкын компонентлары арасында ара 1,25 мм. Кисәк компонентлары, согы, соци һәм ялкын компонентлары арасында ара 1,25 мм. 2,5 мм, Плcc һәм ялкын компонентлары, соя һәм qfp арасында. 4 мм плк. Plcc olкккеткаларын проектлау, ПЛКК рокеты зурлыгына рөхсәт итәр өчен, кайгырту алынырга тиеш (PLCC PIN-ны розетка төбендә).

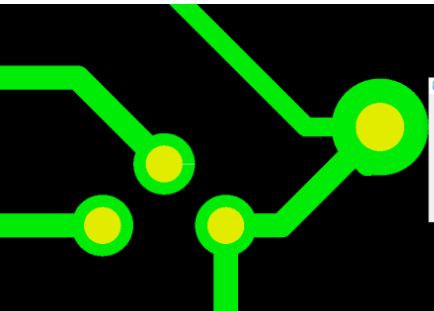

6. Line киңлеге / линия арасы

Дизайнерлар өчен, дизайн процессында без проект таләпләренең төгәллеген һәм камиллеген генә һәм камиллеген генә карый алмыйбыз, зур чикләү - җитештерү процессы. Яхшы продукт туу өчен яңа җитештерү линиясе булдыру мөмкин түгел.

Нормаль шартларда аскы сызыкның сызыгы 4/4мил белән идарә ителә, тишек 8мил (0,2 мм) итеп сайлана. Нигездә, PCB җитештерүчеләрнең 80% тан артыгы җитештерә ала, җитештерү бәясе иң түбән. Минималь сызыкның киңлеге һәм линия дистанциясен 3/4 3мил белән контрольдә тотарга мөмкин, һәм 6мил (0,15 мм) тишек аша сайланырга мөмкин. Нигездә, 70% тан артык машина җитештерүче аны җитештерә ала, ләкин бәя беренче очрактан бераз югарырак, артык күпкә югарырак түгел.

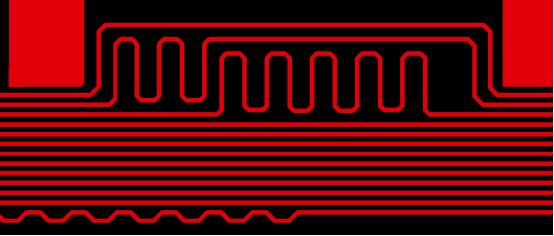

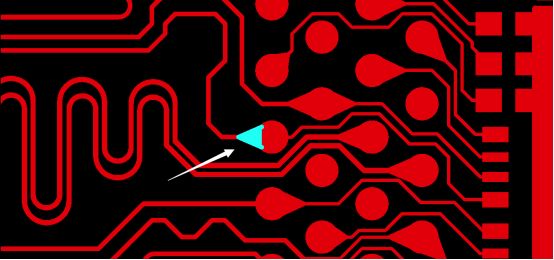

7. Кискен почмак / дөрес почмак

Charp Angle маршрутында гадәттә чыбыклы почмаклар, дөрес почмакта маршрут гадәттә, компьютердагы хәлдән саклану таләп ителә, һәм чыбык сыйфатын үлчәү стандартларына әйләнде. Сигналның бөтенлеге кагылганга, уң почмак чыбыклы чыбыклы паразитик сыйдырышлык һәм индуктивлык тудырачак.

PCB тәлинкә ясау процессында PCB чыбыклары кискен почмакта кисешкәндә, кислотасы почмак дип аталган проблема тудырачак. PCB схемасында Ectb Схеманың артык коррозиясе "кислота почмагы" нда булачак, нәтиҗәдә виртуаль тәнәфес проблемасы. Шуңа күрә, PCB инженерлары чыбыктагы үткен яки сәер почмактан сакланырга, чыбык почмагында 45 градус почмакны сакларга тиеш.

8.Коппер полосасы / утрау

Әгәр дә ул зур утрау булса, ул антенна булыр, бу шау-шу һәм башка комачаулый (чөнки бакыр җиргә китерергә мөмкин - ул сигнал җыючы булачак).

Бакыр полосалары һәм утраулары - ирекле тростта кайбер җитди проблемалар тудырырга мөмкин булган бик күп яссы бакыр катламы. Кечкенә бакыр урыннары PCB панелен өзеп, кыскача схемага китереп, панельдәге башка юнәлешләргә сәяхәт иттеләр.

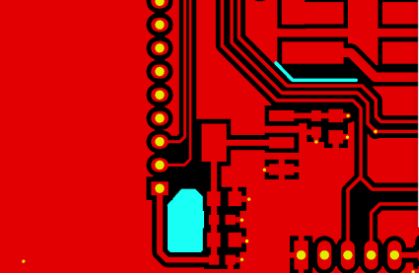

9сы бораулау тишекләре

Тишек шыңгырау бораулау тише тирәсендә бакыр боҗрасын аңлата. Бораулау, оча, бакыр яки бакыр койма, калкулыклы тишекнең толерантлары аркасында калган бакыр боҗрасы һәрвакыт яхшы түгәрәк ноктасына бәрелми, бу тишек таң атуына китерергә мөмкин.

Тишек таклыгының бер ягы 3.5милдән зуррак булырга тиеш, һәм плагин чыңы 6милдән зуррак булырга тиеш. Тишек яңгыры бик кечкенә. Productionитештерү һәм җитештерү процессында бораулау тишеге толерантлары һәм юлның тигезләмәсе дә толерантлык бар. Толерантлыкның тайпылышы тишек боҗрасына китерәчәк, ачык схеманы бозу.

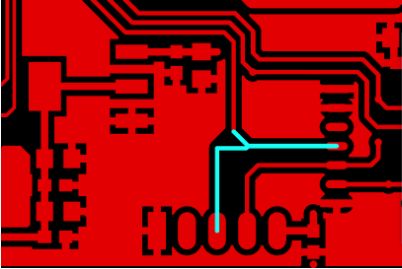

10. Алар чыбыклы тамчылар

PCB чыбыклары өчен күз яшьләрен өстәү PCB чыбыклары PCB тактасы белән тагын да тотрыклы, югары ышанычлылыкны күбрәк ясый ала, шуңа күрә система тотрыклырак булсын өчен, ул район тактага күз яшьләрен өстәргә кирәк.

Күз яшь тамчылары өстәмә чыбыклар белән такта яки чыбык һәм пилот тишеге арасындагы контакт ноктасын өзеклекнең өзелү ноктасыннан өзелүдән сакланырга мөмкин, чөнки район такта зур тышкы көч белән тәэсир иткәндә. Күзләр тамчыларын ашап, падны яклаганда, падрысын сүндерү өчен күп бизәкләрдән сакланырга, җитештерү вакытында тишекне пычраклык аркасында килеп чыккан ярыклардан һәм ярыклардан сакланырга мөмкин.