Dina desain solokan PCB, lapisan tina komponén pentingna, anu nangtukeun darajat dewan sareng panjangna anu tangtu, sareng gaduh dampak sareng jumlah anu tangtu dina réliabilitas kauntungan.

Dewan Vircuit anu hadé, pakaitana terbitan file, tapi ogé mertimbangkeun Emi, ECF (ngaleupaskeun éléktrumik), inténsik Folrosticaty masalah, gipulasi sidang ageung.

Syarat Spésifikasi SMB Washout

1, baca dokrési desain desain, excrozrozo, module khusus, module khusus sareng syarat salak persiapan anu sanés.

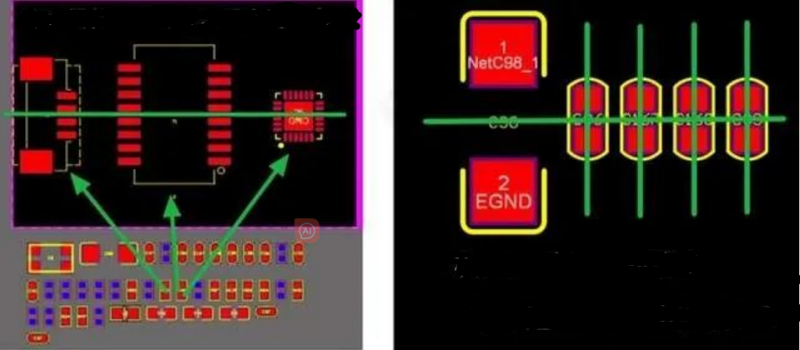

2, Setel titik grid palid ka 25mil, tiasa diblignikeun titik kembang kembang, labing sami; Modeu Alignment ageung sateuacan leutik (alat ageung sareng alat anu ageung diprogram), sareng mode alignment mangrupikeun pusat pusat, sapertos dipidangkeun dina tokoh di handap ieu

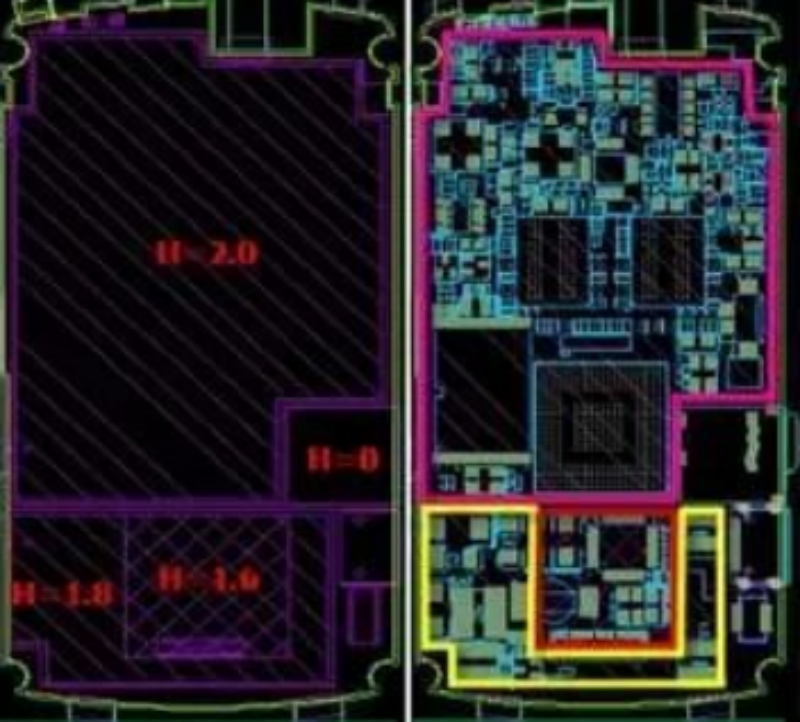

3, pendakian wates tingkat luhureun, struktur sareng perenah khusus, saratorwuma larangan.

° Gambar (kénca) di handap: syarat wates jangkung, ditandaan jelas dina lapisan mékanis atanapi dua lapisan nandaan, merentas kanggo cék crosc cross-engké;

(2) sateuacan lapisan, nyetél daérah anu dilarang, unggal alat janten 5mm jauheun sésa, henteu laponan alat, ijin daék desktey anu bakal nambihan prosés;

Salaku lapisan struktur sareng alat khusus tiasa diposisikan ku koordinat atanapi koordinat pigura luar atanapi garis tengah tina komponén.

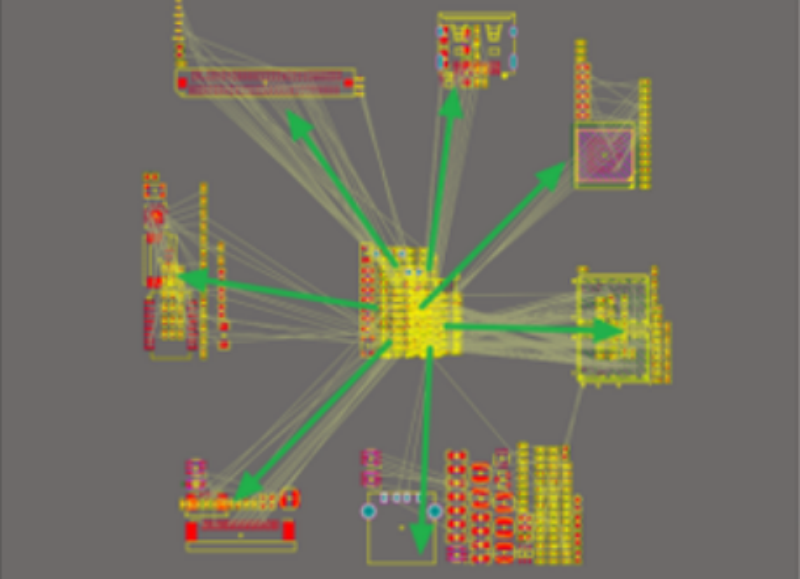

4, perenah kedah gaduh pre-wout heula, ulah kéngingkeun papan pikeun ngamimitian perenah luka langsung, teras dumasar kana serat alkarérna, ukuranana barang modul. Gambar garis akuxily lebar 40mil, sareng ngira-ngira jaga dumasar kana transnhity antara modul dinapasi sareng modul, sapertos anu dipidangkeun dina sosok di handap ieu.

, Perenah kedah ningal tambihan éta daun gurat kakuatan, matak henteu kedah maskas teuing béda, ngalangkungan tangkal listrik

6, komponén termal (saperti kapasitikasi éléktrolis, ototal kristal) perenah kedah jauh tina pasokan listrik anu sanés, sajauh mungkin aya dina liang termal anu sanés, sajauh mungkin aya dina tangkal luhur

7, pikeun nyumponan éksternal peka panyawat, kasaimbangan peribatan saham, sadayana warga skor aliran dielompok

Saga luhur sareng sinyal anyar-ayeuna dipisahkeun tina sinyal lemah tina currents alit sareng vakses anu rendah. Bagian sabagian tegangan anu jarang kaluar dina sadaya lapisan tanpa tambaga tambahan. Jarak ngarayu antara bagian voltasi tinggi anu dipariksa saluyu sareng tabel standar

Sinyal analog di pisah tina sinyal digital kalayan lebar dina dina sahenteuna sahenteuna 20mil, sareng analisa sareng RF.

Sinyal nubasa luhur dipisahkeun tina sinyal frékuénsi lender, jarak misah sahenteuna 3mm, sareng perenah cross teu tiasa dijamin

Lalka alat sinyal sapertos konflikator sareng supir beus kedah jauh ti perenah sirkuit sirkoast, henteu aya dina ujung papan, sareng sahenteuna 10mm. Ostrillator sareng kristal bakal disimpen caket chip, disimpen dina lapisan anu sami, ulah punch liang, sareng cagar jalan pikeun taneuh

Struktur anu sami nuntut "simetris" simétris "(langsung dianggo modul anu sami) pikeun nyumponan konsistén

Saatos desain PCB, urang kedah ngalakukeun sareng paniiti pikeun ngadamel produksi langkung lemes.