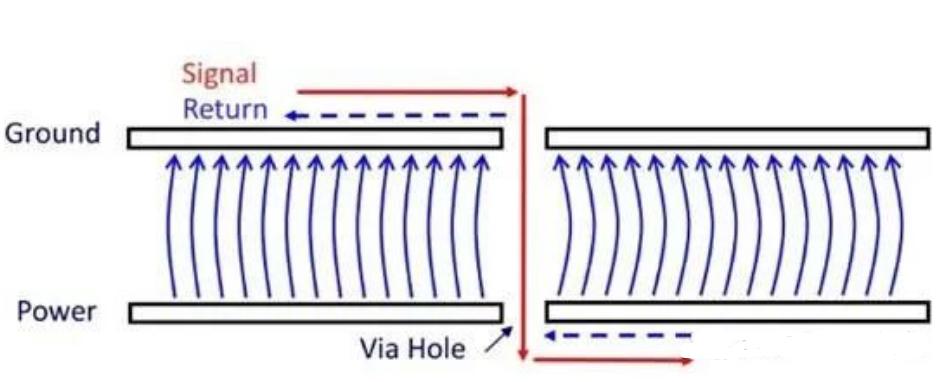

Lamun capacitance interlayer teu cukup badag, médan listrik bakal disebarkeun ngaliwatan wewengkon rélatif badag dewan, ku kituna impedansi interlayer diréduksi jeung arus balik bisa ngalir deui ka lapisan luhur. Dina hal ieu, médan nu dihasilkeun ku sinyal ieu bisa ngaganggu widang sinyal lapisan robah caket dieu. Ieu sanés anu urang ngarepkeun pisan. Hanjakalna, dina papan 4-lapisan 0,062 inci, lapisanna jauh sareng kapasitansi interlayer leutik.

Nalika wiring robah tina lapisan 1 ka Lapisan 4 atawa sabalikna, lajeng bakal ngakibatkeun masalah ieu ditémbongkeun saperti gambar.

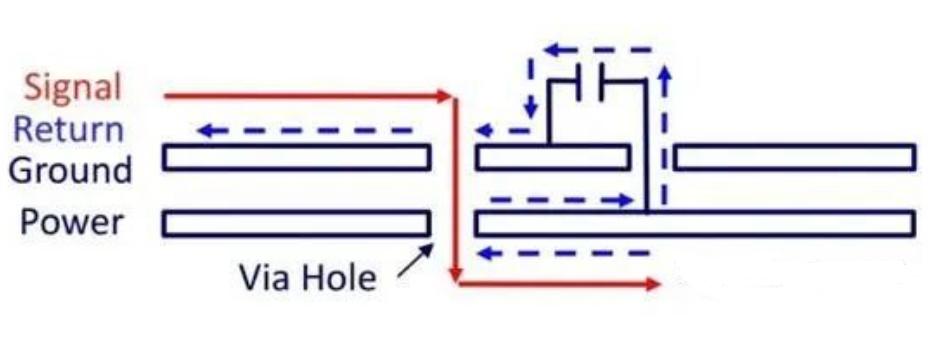

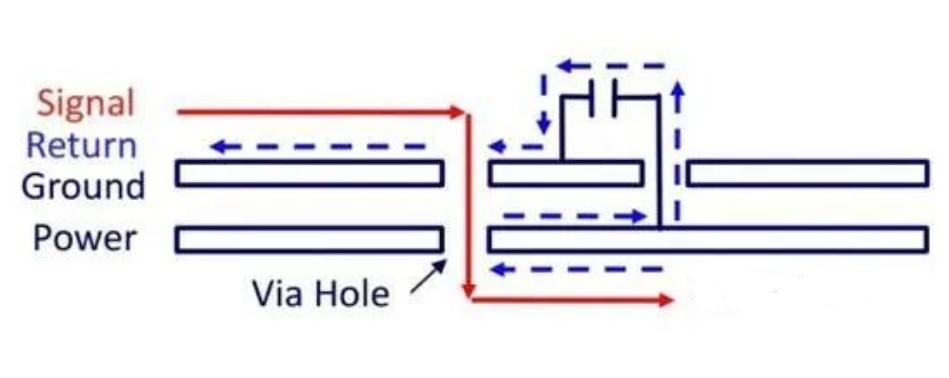

Diagram nunjukeun yen lamun sinyal ngalacak ti lapisan 1 nepi ka lapisan 4 (garis beureum), arus balik ogé kudu ngarobah pesawat (garis biru). Lamun frékuénsi sinyal cukup luhur sarta planes anu deukeut babarengan, arus balik bisa ngalir ngaliwatan capacitance interlayer nu aya antara lapisan taneuh jeung lapisan kakuatan. Sanajan kitu, alatan kurangna sambungan conductive langsung pikeun arus balik, jalur balik interrupted, sarta kami bisa mikir interupsi ieu salaku impedansi antara planes ditémbongkeun saperti gambar di handap ieu.

Lamun capacitance interlayer teu cukup badag, médan listrik bakal disebarkeun ngaliwatan wewengkon rélatif badag dewan, ku kituna impedansi interlayer diréduksi jeung arus balik bisa ngalir deui ka lapisan luhur. Dina hal ieu, médan nu dihasilkeun ku sinyal ieu bisa ngaganggu widang sinyal lapisan robah caket dieu. Ieu sanés anu urang ngarepkeun pisan. Hanjakal, dina dewan 4-lapisan 0,062 inci, lapisan anu tebih eta (sahenteuna 0,020 inci), sarta interlayer capacitance leutik. Hasilna, gangguan médan listrik ditétélakeun di luhur lumangsung. Ieu bisa jadi teu ngabalukarkeun masalah integritas sinyal, tapi pasti bakal nyieun leuwih EMI. Ieu sababna, nalika nganggo kaskade, urang nyingkahan ngarobih lapisan, khususna pikeun sinyal frekuensi tinggi sapertos jam.

Ieu prakték umum pikeun nambahkeun hiji kapasitor decoupling deukeut liang pass transisi pikeun ngurangan impedansi ngalaman ku arus balik ditémbongkeun saperti gambar di handap ieu. Tapi, kapasitor decoupling ieu teu epektip pikeun sinyal VHF alatan frékuénsi timer resonant na low. Pikeun sinyal AC kalawan frékuénsi luhur batan 200-300 MHz, urang teu bisa ngandelkeun decoupling kapasitor pikeun nyieun hiji low-impedansi balik jalur. Kituna, urang kudu decoupling kapasitor (pikeun handap 200-300 MHz) sarta interboard kapasitor rélatif badag pikeun frékuénsi luhur.

Masalah ieu tiasa dihindari ku henteu ngarobih lapisan sinyal konci. Sanajan kitu, kapasitansi interboard leutik tina dewan opat-lapisan ngabalukarkeun masalah serius sejen: transmisi kakuatan. Jam digital ics biasana merlukeun arus catu daya transien badag. Salaku naékna / ragrag waktu kaluaran IC nurun, urang kudu nganteurkeun énergi dina laju nu leuwih luhur. Pikeun nyadiakeun sumber muatan, urang biasana nempatkeun decoupling kapasitor deukeut pisan unggal IC logika. Sanajan kitu, aya masalah: lamun urang balik saluareun frékuénsi timer resonant, decoupling kapasitor teu bisa éfisién nyimpen sarta mindahkeun énergi, sabab dina frékuénsi ieu kapasitor bakal meta kawas hiji induktor.

Kusabab paling ics kiwari boga naékna gancang / kali ragrag (kira-kira 500 ps), urang peryogi hiji struktur decoupling tambahan kalayan frékuénsi timer resonant leuwih luhur ti éta tina kapasitor decoupling. The interlayer capacitance of a circuit board bisa jadi hiji struktur decoupling éféktif, disadiakeun yén lapisan anu cukup deukeut ka silih nyadiakeun capacitance cukup. Ku alatan éta, sajaba kapasitor decoupling ilahar dipaké, urang leuwih resep ngagunakeun lapisan kakuatan raket spasi tur lapisan taneuh pikeun nyadiakeun kakuatan fana ka ics digital.

Punten dicatet yén alatan prosés manufaktur circuit board umum, urang biasana teu boga insulators ipis antara lapisan kadua jeung katilu tina dewan opat-lapisan. Papan opat lapis sareng insulator ipis antara lapisan kadua sareng katilu tiasa langkung mahal tibatan papan opat lapis konvensional.