Când facețiRutare PCB, Din cauza lucrărilor de analiză preliminară nu se face sau nu se face, post-procesarea este dificilă. Dacă placa PCB este comparată cu orașul nostru, componentele sunt ca un rând pe rând de tot felul de clădiri, liniile de semnal sunt străzi și alei din oraș, insula giratorie flyover, apariția fiecărui drum este planificarea sa detaliată, cablarea este de asemenea aceeași.

1.. Cerințe prioritare de cablare

A) Sunt preferate liniile de semnal cheie: sursa de alimentare, semnalul mic analogic, semnalul de mare viteză, semnalul de ceas, semnalul de sincronizare și alte semnale cheie.

B) Principiul priorității densității cablurilor: începeți cablarea din componentă cu cea mai complexă relație de conectare de pe tablă. Cablarea pornește din zona cea mai dens conectată de pe tablă.

C) Precauții pentru procesarea semnalului cheie: încercați să furnizați un strat special de cablare pentru semnale cheie, cum ar fi semnalul de ceas, semnalul de înaltă frecvență și semnalul sensibil și asigurați-vă zona minimă a buclei. Dacă este necesar, ar trebui adoptată protejarea și creșterea distanței de siguranță. Asigurați calitatea semnalului.

D) Rețeaua cu cerințe de control al impedanței trebuie să fie aranjată pe stratul de control al impedanței, iar diviziunea sa de semnal va fi evitată.

2.Controlul scramblerului de cablare

A) Interpretarea principiului 3W

Distanța dintre linii trebuie să fie de 3 ori lățimea liniei. Pentru a reduce intersecția între linii, distanța de linie ar trebui să fie suficient de mare. Dacă distanța centrală a liniei nu este mai mică de 3 ori mai mare decât lățimea liniei, 70% din câmpul electric între linii pot fi păstrate fără interferențe, care se numește regula 3W.

B) Control de modificare: Crosstalk se referă la interferența reciprocă între diferite rețele de pe PCB cauzate de cablarea paralelă lungă, în principal datorită acțiunii capacității distribuite și a inductanței distribuite între liniile paralele. Principalele măsuri pentru a depăși Crosstalk sunt:

I. Creșteți distanța de cabluri paralele și urmați regula 3W;

Ii. Introduceți cabluri de izolare la sol între cablurile paralele

Iii. Reduceți distanța dintre stratul de cablare și planul solului.

3. Reguli generale pentru cerințele de cablare

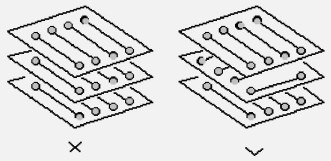

A) Direcția planului adiacent este ortogonală. Evitați diferitele linii de semnal din stratul adiacent în aceeași direcție pentru a reduce modificarea inutilă a straturilor; Dacă această situație este dificil de evitat din cauza limitărilor structurii bordului (cum ar fi unele planuri din spate), mai ales atunci când rata semnalului este mare, ar trebui să luați în considerare izolarea straturilor de cablare pe planul solului și cablurile de semnal pe sol.

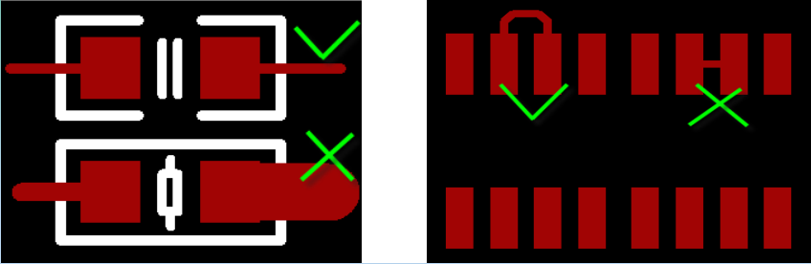

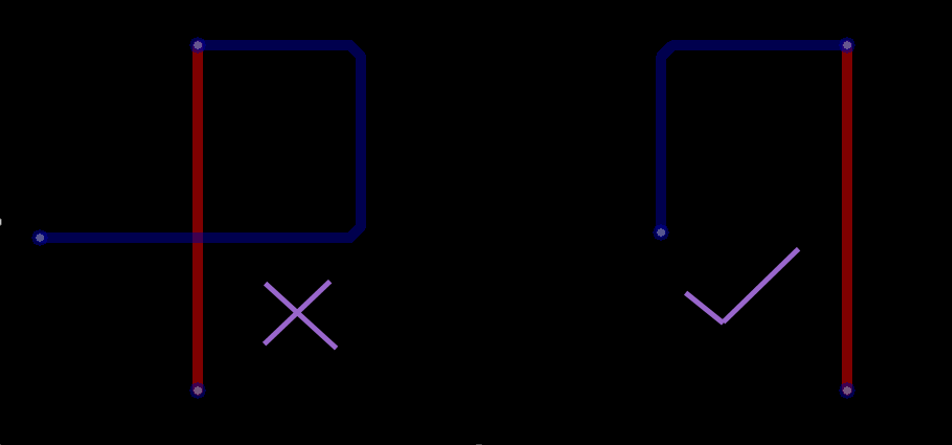

B) Cablarea unor dispozitive mici discrete trebuie să fie simetrică, iar plăcile SMT cu o distanță relativ apropiată ar trebui să fie conectată din exteriorul plăcuței. Conexiunea directă în mijlocul plăcuței nu este permisă.

C) Regula buclă minimă, adică zona buclei formate de linia de semnal și bucla sa ar trebui să fie cât mai mică. Cu cât este mai mică suprafața buclei, cu atât radiația externă este mai mică și cu atât interferența externă este mai mică.

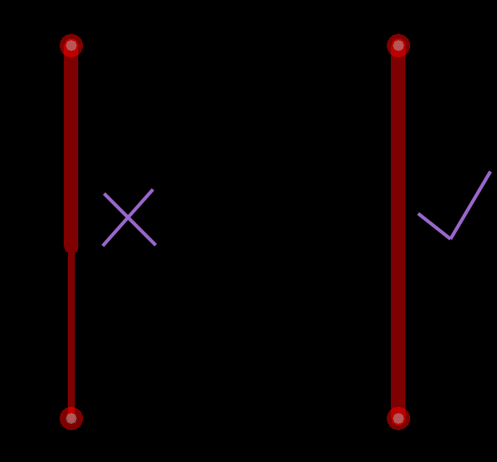

D) cablurile cu ciot nu sunt permise

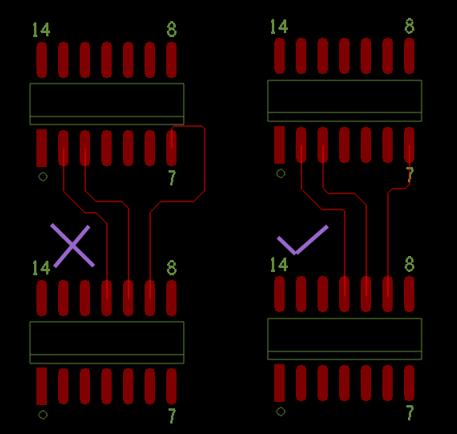

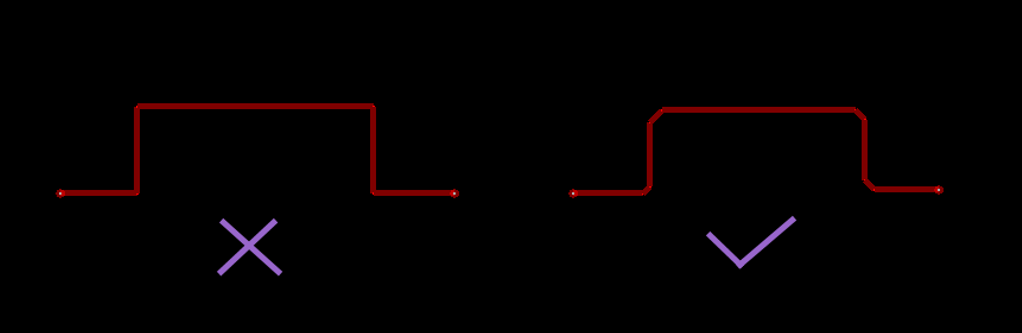

E) Lățimea cablajului din aceeași rețea ar trebui să fie păstrată aceeași. Variația lățimii cablajului va provoca impedanța caracteristică inegală a liniei. Când viteza de transmisie este ridicată, se va produce reflecție. În anumite condiții, cum ar fi firul de plumb al conectorului, o structură similară a sârmei de plumb al pachetului BGA, din cauza distanței mici, poate să nu poată evita schimbarea lățimii liniei, ar trebui să încerce să reducă lungimea efectivă a părții neconcordante din mijloc.

F) Preveniți cablurile de semnal să formeze bucle de sine între diferite straturi. Acest tip de problemă este ușor de avut loc în proiectarea plăcilor multistrat, iar bucla de sine va provoca interferențe de radiații.

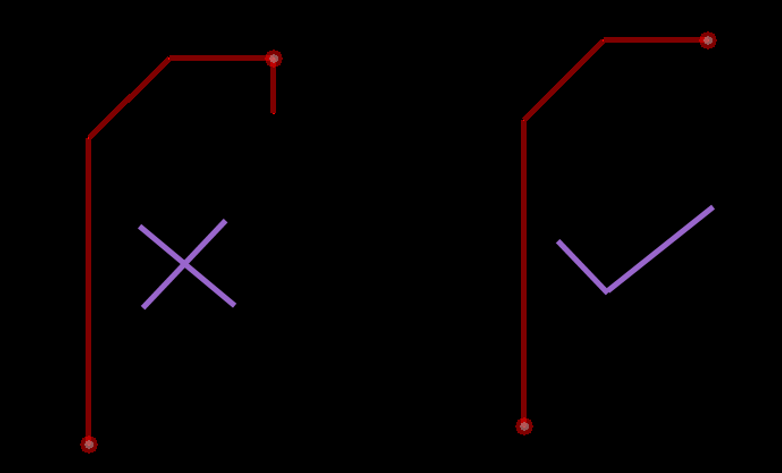

G) unghiul acut și unghiul drept trebuie evitat înProiectare PCB, rezultând radiații inutile și performanța procesului de producție aPCBnu este bun.