ਵਾਇਆ ਮਲਟੀ-ਲੇਅਰ ਪੀਸੀਬੀ ਦੇ ਮਹੱਤਵਪੂਰਨ ਹਿੱਸਿਆਂ ਵਿੱਚੋਂ ਇੱਕ ਹੈ, ਅਤੇ ਡ੍ਰਿਲਿੰਗ ਦੀ ਲਾਗਤ ਆਮ ਤੌਰ 'ਤੇ ਪੀਸੀਬੀ ਬੋਰਡ ਦੀ ਲਾਗਤ ਦੇ 30% ਤੋਂ 40% ਤੱਕ ਹੁੰਦੀ ਹੈ। ਸਧਾਰਨ ਰੂਪ ਵਿੱਚ, ਪੀਸੀਬੀ ਦੇ ਹਰ ਮੋਰੀ ਨੂੰ ਇੱਕ ਰਾਹੀਂ ਕਿਹਾ ਜਾ ਸਕਦਾ ਹੈ।

ਦੁਆਰਾ ਦੀ ਬੁਨਿਆਦੀ ਧਾਰਨਾ:

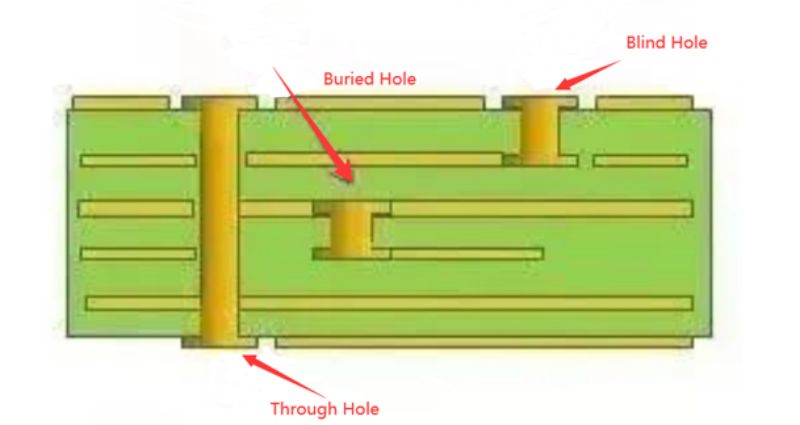

ਫੰਕਸ਼ਨ ਦੇ ਦ੍ਰਿਸ਼ਟੀਕੋਣ ਤੋਂ, via ਨੂੰ ਦੋ ਸ਼੍ਰੇਣੀਆਂ ਵਿੱਚ ਵੰਡਿਆ ਜਾ ਸਕਦਾ ਹੈ: ਇੱਕ ਨੂੰ ਲੇਅਰਾਂ ਦੇ ਵਿਚਕਾਰ ਇੱਕ ਇਲੈਕਟ੍ਰੀਕਲ ਕਨੈਕਸ਼ਨ ਵਜੋਂ ਵਰਤਿਆ ਜਾਂਦਾ ਹੈ, ਅਤੇ ਦੂਜਾ ਡਿਵਾਈਸ ਦੀ ਫਿਕਸਿੰਗ ਜਾਂ ਸਥਿਤੀ ਦੇ ਤੌਰ ਤੇ ਵਰਤਿਆ ਜਾਂਦਾ ਹੈ। ਜੇ ਪ੍ਰਕਿਰਿਆ ਤੋਂ, ਇਹਨਾਂ ਛੇਕਾਂ ਨੂੰ ਆਮ ਤੌਰ 'ਤੇ ਤਿੰਨ ਸ਼੍ਰੇਣੀਆਂ ਵਿੱਚ ਵੰਡਿਆ ਜਾਂਦਾ ਹੈ, ਅਰਥਾਤ ਅੰਨ੍ਹੇ ਛੇਕ, ਦੱਬੇ ਹੋਏ ਛੇਕ ਅਤੇ ਛੇਕ ਦੁਆਰਾ।

ਅੰਨ੍ਹੇ ਛੇਕ ਪ੍ਰਿੰਟ ਕੀਤੇ ਸਰਕਟ ਬੋਰਡ ਦੇ ਉੱਪਰ ਅਤੇ ਹੇਠਲੇ ਸਤਹਾਂ 'ਤੇ ਸਥਿਤ ਹੁੰਦੇ ਹਨ ਅਤੇ ਸਤਹ ਸਰਕਟ ਅਤੇ ਹੇਠਾਂ ਅੰਦਰੂਨੀ ਸਰਕਟ ਦੇ ਕੁਨੈਕਸ਼ਨ ਲਈ ਇੱਕ ਖਾਸ ਡੂੰਘਾਈ ਹੁੰਦੀ ਹੈ, ਅਤੇ ਛੇਕਾਂ ਦੀ ਡੂੰਘਾਈ ਆਮ ਤੌਰ 'ਤੇ ਇੱਕ ਖਾਸ ਅਨੁਪਾਤ (ਅਪਰਚਰ) ਤੋਂ ਵੱਧ ਨਹੀਂ ਹੁੰਦੀ ਹੈ।

ਦੱਬਿਆ ਹੋਇਆ ਮੋਰੀ ਪ੍ਰਿੰਟਿਡ ਸਰਕਟ ਬੋਰਡ ਦੀ ਅੰਦਰਲੀ ਪਰਤ ਵਿੱਚ ਸਥਿਤ ਕੁਨੈਕਸ਼ਨ ਮੋਰੀ ਨੂੰ ਦਰਸਾਉਂਦਾ ਹੈ, ਜੋ ਬੋਰਡ ਦੀ ਸਤ੍ਹਾ ਤੱਕ ਨਹੀਂ ਫੈਲਦਾ ਹੈ। ਉਪਰੋਕਤ ਦੋ ਤਰ੍ਹਾਂ ਦੇ ਛੇਕ ਸਰਕਟ ਬੋਰਡ ਦੀ ਅੰਦਰਲੀ ਪਰਤ ਵਿੱਚ ਸਥਿਤ ਹੁੰਦੇ ਹਨ, ਜੋ ਲੈਮੀਨੇਸ਼ਨ ਤੋਂ ਪਹਿਲਾਂ ਥਰੂ ਹੋਲ ਮੋਲਡਿੰਗ ਪ੍ਰਕਿਰਿਆ ਦੁਆਰਾ ਪੂਰਾ ਕੀਤਾ ਜਾਂਦਾ ਹੈ, ਅਤੇ ਥਰੂ ਹੋਲ ਦੇ ਗਠਨ ਦੌਰਾਨ ਕਈ ਅੰਦਰੂਨੀ ਪਰਤਾਂ ਓਵਰਲੈਪ ਹੋ ਸਕਦੀਆਂ ਹਨ।

ਤੀਜੀ ਕਿਸਮ ਨੂੰ ਥਰੂ-ਹੋਲ ਕਿਹਾ ਜਾਂਦਾ ਹੈ, ਜੋ ਪੂਰੇ ਸਰਕਟ ਬੋਰਡ ਵਿੱਚੋਂ ਲੰਘਦੇ ਹਨ ਅਤੇ ਅੰਦਰੂਨੀ ਇੰਟਰਕਨੈਕਸ਼ਨ ਨੂੰ ਪ੍ਰਾਪਤ ਕਰਨ ਲਈ ਜਾਂ ਕੰਪੋਨੈਂਟਸ ਲਈ ਇੰਸਟਾਲੇਸ਼ਨ ਪੋਜੀਸ਼ਨਿੰਗ ਹੋਲ ਵਜੋਂ ਵਰਤਿਆ ਜਾ ਸਕਦਾ ਹੈ। ਕਿਉਂਕਿ ਪ੍ਰਕਿਰਿਆ ਵਿੱਚ ਹੋਲ ਰਾਹੀਂ ਪ੍ਰਾਪਤ ਕਰਨਾ ਆਸਾਨ ਹੁੰਦਾ ਹੈ ਅਤੇ ਲਾਗਤ ਘੱਟ ਹੁੰਦੀ ਹੈ, ਇਸ ਲਈ ਜ਼ਿਆਦਾਤਰ ਪ੍ਰਿੰਟ ਕੀਤੇ ਸਰਕਟ ਬੋਰਡ ਇਸਦੀ ਵਰਤੋਂ ਕਰਦੇ ਹਨ, ਨਾ ਕਿ ਹੋਰ ਦੋ ਮੋਰੀਆਂ ਰਾਹੀਂ। ਹੇਠ ਦਿੱਤੇ ਛੇਕ, ਬਿਨਾਂ ਵਿਸ਼ੇਸ਼ ਨਿਰਦੇਸ਼ਾਂ ਦੇ, ਛੇਕ ਦੁਆਰਾ ਮੰਨਿਆ ਜਾਂਦਾ ਹੈ।

ਡਿਜ਼ਾਇਨ ਦੇ ਦ੍ਰਿਸ਼ਟੀਕੋਣ ਤੋਂ, ਇੱਕ via ਮੁੱਖ ਤੌਰ 'ਤੇ ਦੋ ਹਿੱਸਿਆਂ ਦਾ ਬਣਿਆ ਹੁੰਦਾ ਹੈ, ਇੱਕ ਡ੍ਰਿਲਿੰਗ ਮੋਰੀ ਦੇ ਵਿਚਕਾਰ ਹੁੰਦਾ ਹੈ, ਅਤੇ ਦੂਜਾ ਡਿਰਲ ਹੋਲ ਦੇ ਆਲੇ ਦੁਆਲੇ ਵੈਲਡਿੰਗ ਪੈਡ ਖੇਤਰ ਹੁੰਦਾ ਹੈ। ਇਹਨਾਂ ਦੋ ਹਿੱਸਿਆਂ ਦਾ ਆਕਾਰ ਦੁਆਰਾ ਦਾ ਆਕਾਰ ਨਿਰਧਾਰਤ ਕਰਦਾ ਹੈ.

ਸਪੱਸ਼ਟ ਤੌਰ 'ਤੇ, ਹਾਈ-ਸਪੀਡ, ਉੱਚ-ਘਣਤਾ ਵਾਲੇ ਪੀਸੀਬੀ ਡਿਜ਼ਾਈਨ ਵਿੱਚ, ਡਿਜ਼ਾਈਨਰ ਹਮੇਸ਼ਾ ਮੋਰੀ ਨੂੰ ਜਿੰਨਾ ਸੰਭਵ ਹੋ ਸਕੇ ਛੋਟਾ ਚਾਹੁੰਦੇ ਹਨ, ਤਾਂ ਜੋ ਹੋਰ ਵਾਇਰਿੰਗ ਸਪੇਸ ਛੱਡੀ ਜਾ ਸਕੇ, ਇਸ ਤੋਂ ਇਲਾਵਾ, ਵਾਇਆ ਜਿੰਨਾ ਛੋਟਾ, ਇਸਦਾ ਆਪਣਾ ਪਰਜੀਵੀ ਸਮਰੱਥਾ ਛੋਟਾ, ਵਧੇਰੇ ਅਨੁਕੂਲ ਹੈ। ਹਾਈ-ਸਪੀਡ ਸਰਕਟਾਂ ਲਈ.

ਹਾਲਾਂਕਿ, ਵਾਇਆ ਆਕਾਰ ਦੀ ਕਮੀ ਲਾਗਤਾਂ ਵਿੱਚ ਵਾਧਾ ਵੀ ਲਿਆਉਂਦੀ ਹੈ, ਅਤੇ ਮੋਰੀ ਦੇ ਆਕਾਰ ਨੂੰ ਅਣਮਿੱਥੇ ਸਮੇਂ ਲਈ ਨਹੀਂ ਘਟਾਇਆ ਜਾ ਸਕਦਾ, ਇਹ ਡਿਰਲ ਅਤੇ ਇਲੈਕਟ੍ਰੋਪਲੇਟਿੰਗ ਤਕਨਾਲੋਜੀ ਦੁਆਰਾ ਸੀਮਿਤ ਹੈ: ਮੋਰੀ ਜਿੰਨਾ ਛੋਟਾ ਹੋਵੇਗਾ, ਡ੍ਰਿਲਿੰਗ ਵਿੱਚ ਜਿੰਨਾ ਜ਼ਿਆਦਾ ਸਮਾਂ ਲੱਗੇਗਾ, ਓਨਾ ਹੀ ਸੌਖਾ ਹੈ। ਕੇਂਦਰ ਤੋਂ ਭਟਕਣਾ ਹੈ; ਜਦੋਂ ਮੋਰੀ ਦੀ ਡੂੰਘਾਈ ਮੋਰੀ ਦੇ ਵਿਆਸ ਤੋਂ 6 ਗੁਣਾ ਵੱਧ ਹੁੰਦੀ ਹੈ, ਤਾਂ ਇਹ ਸੁਨਿਸ਼ਚਿਤ ਕਰਨਾ ਅਸੰਭਵ ਹੁੰਦਾ ਹੈ ਕਿ ਮੋਰੀ ਦੀ ਕੰਧ ਨੂੰ ਤਾਂਬੇ ਨਾਲ ਇੱਕਸਾਰ ਰੂਪ ਵਿੱਚ ਪਲੇਟ ਕੀਤਾ ਜਾ ਸਕਦਾ ਹੈ।

ਉਦਾਹਰਨ ਲਈ, ਜੇਕਰ ਇੱਕ ਸਾਧਾਰਨ 6-ਲੇਅਰ PCB ਬੋਰਡ ਦੀ ਮੋਟਾਈ (ਮੋਰੀ ਡੂੰਘਾਈ ਦੁਆਰਾ) 50Mil ਹੈ, ਤਾਂ ਘੱਟੋ-ਘੱਟ ਡ੍ਰਿਲਿੰਗ ਵਿਆਸ ਜੋ PCB ਨਿਰਮਾਤਾ ਆਮ ਹਾਲਤਾਂ ਵਿੱਚ ਪ੍ਰਦਾਨ ਕਰ ਸਕਦੇ ਹਨ ਸਿਰਫ 8Mil ਤੱਕ ਪਹੁੰਚ ਸਕਦਾ ਹੈ। ਲੇਜ਼ਰ ਡ੍ਰਿਲਿੰਗ ਤਕਨਾਲੋਜੀ ਦੇ ਵਿਕਾਸ ਦੇ ਨਾਲ, ਡ੍ਰਿਲਿੰਗ ਦਾ ਆਕਾਰ ਵੀ ਛੋਟਾ ਅਤੇ ਛੋਟਾ ਹੋ ਸਕਦਾ ਹੈ, ਅਤੇ ਮੋਰੀ ਦਾ ਵਿਆਸ ਆਮ ਤੌਰ 'ਤੇ 6Mils ਤੋਂ ਘੱਟ ਜਾਂ ਬਰਾਬਰ ਹੁੰਦਾ ਹੈ, ਸਾਨੂੰ ਮਾਈਕ੍ਰੋਹੋਲ ਕਿਹਾ ਜਾਂਦਾ ਹੈ।

ਮਾਈਕ੍ਰੋਹੋਲ ਅਕਸਰ HDI (ਉੱਚ ਘਣਤਾ ਇੰਟਰਕਨੈਕਟ ਬਣਤਰ) ਡਿਜ਼ਾਈਨ ਵਿੱਚ ਵਰਤੇ ਜਾਂਦੇ ਹਨ, ਅਤੇ ਮਾਈਕ੍ਰੋਹੋਲ ਤਕਨਾਲੋਜੀ ਮੋਰੀ ਨੂੰ ਸਿੱਧੇ ਪੈਡ 'ਤੇ ਡ੍ਰਿਲ ਕਰਨ ਦੀ ਇਜਾਜ਼ਤ ਦੇ ਸਕਦੀ ਹੈ, ਜੋ ਸਰਕਟ ਦੀ ਕਾਰਗੁਜ਼ਾਰੀ ਨੂੰ ਬਹੁਤ ਸੁਧਾਰਦਾ ਹੈ ਅਤੇ ਵਾਇਰਿੰਗ ਸਪੇਸ ਨੂੰ ਬਚਾਉਂਦਾ ਹੈ। via ਟਰਾਂਸਮਿਸ਼ਨ ਲਾਈਨ 'ਤੇ ਅੜਿੱਕਾ ਬੰਦ ਹੋਣ ਦੇ ਬ੍ਰੇਕਪੁਆਇੰਟ ਵਜੋਂ ਦਿਖਾਈ ਦਿੰਦਾ ਹੈ, ਜਿਸ ਨਾਲ ਸਿਗਨਲ ਦਾ ਪ੍ਰਤੀਬਿੰਬ ਹੁੰਦਾ ਹੈ। ਆਮ ਤੌਰ 'ਤੇ, ਮੋਰੀ ਦਾ ਬਰਾਬਰ ਪ੍ਰਤੀਰੋਧ ਟਰਾਂਸਮਿਸ਼ਨ ਲਾਈਨ ਨਾਲੋਂ ਲਗਭਗ 12% ਘੱਟ ਹੁੰਦਾ ਹੈ, ਉਦਾਹਰਨ ਲਈ, ਇੱਕ 50 ohms ਟ੍ਰਾਂਸਮਿਸ਼ਨ ਲਾਈਨ ਦੀ ਰੁਕਾਵਟ 6 ohms ਦੁਆਰਾ ਘਟਾਈ ਜਾਵੇਗੀ ਜਦੋਂ ਇਹ ਮੋਰੀ ਵਿੱਚੋਂ ਲੰਘਦੀ ਹੈ (ਖਾਸ ਤੌਰ 'ਤੇ ਅਤੇ ਦੁਆਰਾ ਦਾ ਆਕਾਰ, ਪਲੇਟ ਦੀ ਮੋਟਾਈ ਵੀ ਸੰਬੰਧਿਤ ਹੈ, ਪੂਰੀ ਕਮੀ ਨਹੀਂ)।

ਹਾਲਾਂਕਿ, ਦੁਆਰਾ ਪ੍ਰਤੀਬਿੰਬ ਦੇ ਵਿਗਾੜ ਕਾਰਨ ਪੈਦਾ ਹੋਇਆ ਪ੍ਰਤੀਬਿੰਬ ਅਸਲ ਵਿੱਚ ਬਹੁਤ ਛੋਟਾ ਹੈ, ਅਤੇ ਇਸਦਾ ਪ੍ਰਤੀਬਿੰਬ ਗੁਣਾਂਕ ਕੇਵਲ ਇਹ ਹੈ:

(44-50)/(44 + 50) = 0.06

ਦੁਆਰਾ ਪੈਦਾ ਹੋਣ ਵਾਲੀਆਂ ਸਮੱਸਿਆਵਾਂ ਪਰਜੀਵੀ ਸਮਰੱਥਾ ਅਤੇ ਪ੍ਰੇਰਕਤਾ ਦੇ ਪ੍ਰਭਾਵਾਂ 'ਤੇ ਵਧੇਰੇ ਕੇਂਦ੍ਰਿਤ ਹਨ।

Via ਦੀ ਪਰਜੀਵੀ ਸਮਰੱਥਾ ਅਤੇ ਇੰਡਕਟੈਂਸ ਦੁਆਰਾ

ਆਪਣੇ ਆਪ ਵਿੱਚ ਇੱਕ ਪਰਜੀਵੀ ਅਵਾਰਾ ਸਮਰੱਥਾ ਹੈ. ਜੇ ਰੱਖੀ ਗਈ ਪਰਤ 'ਤੇ ਸੋਲਡਰ ਪ੍ਰਤੀਰੋਧ ਜ਼ੋਨ ਦਾ ਵਿਆਸ D2 ਹੈ, ਸੋਲਡਰ ਪੈਡ ਦਾ ਵਿਆਸ D1 ਹੈ, ਪੀਸੀਬੀ ਬੋਰਡ ਦੀ ਮੋਟਾਈ T ਹੈ, ਅਤੇ ਸਬਸਟਰੇਟ ਦਾ ਡਾਈਇਲੈਕਟ੍ਰਿਕ ਸਥਿਰਤਾ ε ਹੈ, ਥ੍ਰੂ ਹੋਲ ਦੀ ਪਰਜੀਵੀ ਸਮਰੱਥਾ ਲਗਭਗ ਹੈ:

C=1.41εTD1/(D2-D1)

ਸਰਕਟ 'ਤੇ ਪਰਜੀਵੀ ਸਮਰੱਥਾ ਦਾ ਮੁੱਖ ਪ੍ਰਭਾਵ ਸਿਗਨਲ ਦੇ ਵਧਣ ਦੇ ਸਮੇਂ ਨੂੰ ਲੰਮਾ ਕਰਨਾ ਅਤੇ ਸਰਕਟ ਦੀ ਗਤੀ ਨੂੰ ਘਟਾਉਣਾ ਹੈ।

ਉਦਾਹਰਨ ਲਈ, 50Mil ਦੀ ਮੋਟਾਈ ਵਾਲੇ PCB ਲਈ, ਜੇਕਰ ਪੈਡ ਦੇ ਵਿਆਸ 20Mil (ਡਰਿਲਿੰਗ ਹੋਲ ਦਾ ਵਿਆਸ 10Mil ਹੈ) ਅਤੇ ਸੋਲਡਰ ਪ੍ਰਤੀਰੋਧ ਜ਼ੋਨ ਦਾ ਵਿਆਸ 40Mil ਹੈ, ਤਾਂ ਅਸੀਂ ਪੈਰਾਸਾਈਟਿਕ ਕੈਪੈਸੀਟੈਂਸ ਦਾ ਅੰਦਾਜ਼ਾ ਲਗਾ ਸਕਦੇ ਹਾਂ। ਉਪਰੋਕਤ ਫਾਰਮੂਲੇ ਦੁਆਰਾ:

C=1.41x4.4x0.050x0.020/(0.040-0.020)=0.31pF

ਸਮਰੱਥਾ ਦੇ ਇਸ ਹਿੱਸੇ ਦੇ ਕਾਰਨ ਵਧਣ ਦੇ ਸਮੇਂ ਵਿੱਚ ਤਬਦੀਲੀ ਦੀ ਮਾਤਰਾ ਲਗਭਗ ਹੈ:

T10-90=2.2C(Z0/2)=2.2x0.31x(50/2)=17.05ps

ਇਹਨਾਂ ਮੁੱਲਾਂ ਤੋਂ ਇਹ ਦੇਖਿਆ ਜਾ ਸਕਦਾ ਹੈ ਕਿ ਹਾਲਾਂਕਿ ਸਿੰਗਲ ਵਾਈਅ ਦੀ ਪਰਜੀਵੀ ਸਮਰੱਥਾ ਕਾਰਨ ਹੋਣ ਵਾਲੀ ਉਭਾਰ ਦੇਰੀ ਦੀ ਉਪਯੋਗਤਾ ਬਹੁਤ ਸਪੱਸ਼ਟ ਨਹੀਂ ਹੈ, ਜੇਕਰ ਲੇਅਰਾਂ ਵਿਚਕਾਰ ਸਵਿਚ ਕਰਨ ਲਈ ਲਾਈਨ ਵਿੱਚ ਕਈ ਵਾਰ ਵਿਆ ਦੀ ਵਰਤੋਂ ਕੀਤੀ ਜਾਂਦੀ ਹੈ, ਤਾਂ ਮਲਟੀਪਲ ਹੋਲ ਵਰਤੇ ਜਾਣਗੇ, ਅਤੇ ਡਿਜ਼ਾਈਨ ਨੂੰ ਧਿਆਨ ਨਾਲ ਵਿਚਾਰਿਆ ਜਾਣਾ ਚਾਹੀਦਾ ਹੈ. ਅਸਲ ਡਿਜ਼ਾਇਨ ਵਿੱਚ, ਪਰਜੀਵੀ ਸਮਰੱਥਾ ਨੂੰ ਮੋਰੀ ਅਤੇ ਤਾਂਬੇ ਦੇ ਖੇਤਰ (ਐਂਟੀ-ਪੈਡ) ਵਿਚਕਾਰ ਦੂਰੀ ਵਧਾ ਕੇ ਜਾਂ ਪੈਡ ਦੇ ਵਿਆਸ ਨੂੰ ਘਟਾ ਕੇ ਘਟਾਇਆ ਜਾ ਸਕਦਾ ਹੈ।

ਹਾਈ-ਸਪੀਡ ਡਿਜੀਟਲ ਸਰਕਟਾਂ ਦੇ ਡਿਜ਼ਾਇਨ ਵਿੱਚ, ਪਰਜੀਵੀ ਇੰਡਕਟੈਂਸ ਦੁਆਰਾ ਹੋਣ ਵਾਲਾ ਨੁਕਸਾਨ ਅਕਸਰ ਪਰਜੀਵੀ ਸਮਰੱਥਾ ਦੇ ਪ੍ਰਭਾਵ ਤੋਂ ਵੱਧ ਹੁੰਦਾ ਹੈ। ਇਸ ਦਾ ਪਰਜੀਵੀ ਲੜੀ ਇੰਡਕਟੈਂਸ ਬਾਈਪਾਸ ਕੈਪਸੀਟਰ ਦੇ ਯੋਗਦਾਨ ਨੂੰ ਕਮਜ਼ੋਰ ਕਰ ਦੇਵੇਗੀ ਅਤੇ ਪੂਰੇ ਪਾਵਰ ਸਿਸਟਮ ਦੀ ਫਿਲਟਰਿੰਗ ਪ੍ਰਭਾਵ ਨੂੰ ਕਮਜ਼ੋਰ ਕਰੇਗੀ।

ਅਸੀਂ ਇੱਕ ਥ੍ਰੂ-ਹੋਲ ਅਨੁਮਾਨ ਦੇ ਪਰਜੀਵੀ ਇੰਡਕਟੈਂਸ ਦੀ ਗਣਨਾ ਕਰਨ ਲਈ ਹੇਠਾਂ ਦਿੱਤੇ ਅਨੁਭਵੀ ਫਾਰਮੂਲੇ ਦੀ ਵਰਤੋਂ ਕਰ ਸਕਦੇ ਹਾਂ:

L=5.08h[ln(4h/d)+1]

ਜਿੱਥੇ L via ਦੇ ਇੰਡਕਟੈਂਸ ਨੂੰ ਦਰਸਾਉਂਦਾ ਹੈ, h via ਦੀ ਲੰਬਾਈ ਹੈ, ਅਤੇ d ਕੇਂਦਰੀ ਮੋਰੀ ਦਾ ਵਿਆਸ ਹੈ। ਇਹ ਫਾਰਮੂਲੇ ਤੋਂ ਦੇਖਿਆ ਜਾ ਸਕਦਾ ਹੈ ਕਿ via ਦੇ ਵਿਆਸ ਦਾ ਇੰਡਕਟੈਂਸ 'ਤੇ ਬਹੁਤ ਘੱਟ ਪ੍ਰਭਾਵ ਹੁੰਦਾ ਹੈ, ਜਦੋਂ ਕਿ via ਦੀ ਲੰਬਾਈ ਦਾ ਇੰਡਕਟੈਂਸ 'ਤੇ ਸਭ ਤੋਂ ਵੱਧ ਪ੍ਰਭਾਵ ਹੁੰਦਾ ਹੈ। ਅਜੇ ਵੀ ਉਪਰੋਕਤ ਉਦਾਹਰਨ ਦੀ ਵਰਤੋਂ ਕਰਦੇ ਹੋਏ, ਆਊਟ-ਆਫ-ਹੋਲ ਇੰਡਕਟੈਂਸ ਦੀ ਗਣਨਾ ਇਸ ਤਰ੍ਹਾਂ ਕੀਤੀ ਜਾ ਸਕਦੀ ਹੈ:

L=5.08x0.050[ln(4x0.050/0.010)+1]=1.015nH

ਜੇਕਰ ਸਿਗਨਲ ਦਾ ਵਧਣ ਦਾ ਸਮਾਂ 1ns ਹੈ, ਤਾਂ ਇਸਦਾ ਬਰਾਬਰ ਪ੍ਰਤੀਰੋਧ ਆਕਾਰ ਹੈ:

XL=πL/T10-90=3.19Ω

ਉੱਚ-ਆਵਿਰਤੀ ਵਾਲੇ ਕਰੰਟ ਦੀ ਮੌਜੂਦਗੀ ਵਿੱਚ ਅਜਿਹੇ ਅੜਿੱਕੇ ਨੂੰ ਨਜ਼ਰਅੰਦਾਜ਼ ਨਹੀਂ ਕੀਤਾ ਜਾ ਸਕਦਾ ਹੈ, ਖਾਸ ਤੌਰ 'ਤੇ, ਧਿਆਨ ਦਿਓ ਕਿ ਬਾਈਪਾਸ ਕੈਪਸੀਟਰ ਨੂੰ ਪਾਵਰ ਪਰਤ ਅਤੇ ਗਠਨ ਨੂੰ ਜੋੜਦੇ ਸਮੇਂ ਦੋ ਛੇਕਾਂ ਵਿੱਚੋਂ ਲੰਘਣ ਦੀ ਲੋੜ ਹੁੰਦੀ ਹੈ, ਤਾਂ ਜੋ ਮੋਰੀ ਦੀ ਪਰਜੀਵੀ ਪ੍ਰੇਰਣਾ ਨੂੰ ਗੁਣਾ ਕੀਤਾ ਜਾ ਸਕੇ।

ਦੁਆਰਾ ਦੀ ਵਰਤੋਂ ਕਿਵੇਂ ਕਰੀਏ?

ਮੋਰੀ ਦੀਆਂ ਪਰਜੀਵੀ ਵਿਸ਼ੇਸ਼ਤਾਵਾਂ ਦੇ ਉਪਰੋਕਤ ਵਿਸ਼ਲੇਸ਼ਣ ਦੁਆਰਾ, ਅਸੀਂ ਦੇਖ ਸਕਦੇ ਹਾਂ ਕਿ ਹਾਈ-ਸਪੀਡ ਪੀਸੀਬੀ ਡਿਜ਼ਾਈਨ ਵਿੱਚ, ਪ੍ਰਤੀਤ ਹੁੰਦਾ ਸਧਾਰਨ ਛੇਕ ਅਕਸਰ ਸਰਕਟ ਦੇ ਡਿਜ਼ਾਈਨ 'ਤੇ ਬਹੁਤ ਮਾੜਾ ਪ੍ਰਭਾਵ ਲਿਆਉਂਦਾ ਹੈ। ਮੋਰੀ ਦੇ ਪਰਜੀਵੀ ਪ੍ਰਭਾਵ ਕਾਰਨ ਹੋਣ ਵਾਲੇ ਮਾੜੇ ਪ੍ਰਭਾਵਾਂ ਨੂੰ ਘਟਾਉਣ ਲਈ, ਡਿਜ਼ਾਇਨ ਜਿੱਥੋਂ ਤੱਕ ਸੰਭਵ ਹੋ ਸਕਦਾ ਹੈ:

ਲਾਗਤ ਅਤੇ ਸਿਗਨਲ ਕੁਆਲਿਟੀ ਦੇ ਦੋ ਪਹਿਲੂਆਂ ਤੋਂ, ਦੁਆਰਾ ਆਕਾਰ ਦਾ ਇੱਕ ਵਾਜਬ ਆਕਾਰ ਚੁਣੋ। ਜੇ ਜਰੂਰੀ ਹੋਵੇ, ਤਾਂ ਤੁਸੀਂ ਵੱਖ-ਵੱਖ ਆਕਾਰਾਂ ਦੇ ਵੀਅਸ ਦੀ ਵਰਤੋਂ ਕਰਨ 'ਤੇ ਵਿਚਾਰ ਕਰ ਸਕਦੇ ਹੋ, ਜਿਵੇਂ ਕਿ ਬਿਜਲੀ ਦੀ ਸਪਲਾਈ ਜਾਂ ਜ਼ਮੀਨੀ ਤਾਰ ਦੇ ਛੇਕ ਲਈ, ਤੁਸੀਂ ਰੁਕਾਵਟ ਨੂੰ ਘਟਾਉਣ ਲਈ ਵੱਡੇ ਆਕਾਰ ਦੀ ਵਰਤੋਂ ਕਰਨ 'ਤੇ ਵਿਚਾਰ ਕਰ ਸਕਦੇ ਹੋ, ਅਤੇ ਸਿਗਨਲ ਵਾਇਰਿੰਗ ਲਈ, ਤੁਸੀਂ ਇੱਕ ਛੋਟੇ ਦੁਆਰਾ ਵਰਤ ਸਕਦੇ ਹੋ। ਬੇਸ਼ੱਕ, ਜਿਵੇਂ ਕਿ ਵਾਇਆ ਦਾ ਆਕਾਰ ਘਟਦਾ ਹੈ, ਅਨੁਸਾਰੀ ਲਾਗਤ ਵੀ ਵਧੇਗੀ

ਉੱਪਰ ਦੱਸੇ ਗਏ ਦੋ ਫਾਰਮੂਲਿਆਂ ਤੋਂ ਇਹ ਸਿੱਟਾ ਕੱਢਿਆ ਜਾ ਸਕਦਾ ਹੈ ਕਿ ਇੱਕ ਪਤਲੇ ਪੀਸੀਬੀ ਬੋਰਡ ਦੀ ਵਰਤੋਂ ਦੋ ਪਰਜੀਵੀ ਪੈਰਾਮੀਟਰਾਂ ਨੂੰ ਘਟਾਉਣ ਲਈ ਅਨੁਕੂਲ ਹੈ

ਪੀਸੀਬੀ ਬੋਰਡ 'ਤੇ ਸਿਗਨਲ ਵਾਇਰਿੰਗ ਨੂੰ ਜਿੱਥੋਂ ਤੱਕ ਸੰਭਵ ਹੋ ਸਕੇ ਬਦਲਿਆ ਨਹੀਂ ਜਾਣਾ ਚਾਹੀਦਾ ਹੈ, ਮਤਲਬ ਕਿ ਬੇਲੋੜੀ ਵਿਆਸ ਦੀ ਵਰਤੋਂ ਨਾ ਕਰਨ ਦੀ ਕੋਸ਼ਿਸ਼ ਕਰੋ।

ਵਿਅਸ ਨੂੰ ਪਾਵਰ ਸਪਲਾਈ ਦੇ ਪਿੰਨ ਅਤੇ ਜ਼ਮੀਨ ਵਿੱਚ ਡ੍ਰਿਲ ਕੀਤਾ ਜਾਣਾ ਚਾਹੀਦਾ ਹੈ। ਪਿੰਨ ਅਤੇ ਵਿਅਸ ਵਿਚਕਾਰ ਲੀਡ ਜਿੰਨੀ ਛੋਟੀ ਹੋਵੇਗੀ, ਉੱਨਾ ਹੀ ਵਧੀਆ। ਸਮਾਨ ਇੰਡਕਟੈਂਸ ਨੂੰ ਘਟਾਉਣ ਲਈ ਸਮਾਨਾਂਤਰ ਵਿੱਚ ਕਈ ਛੇਕਾਂ ਨੂੰ ਡ੍ਰਿੱਲ ਕੀਤਾ ਜਾ ਸਕਦਾ ਹੈ।

ਸਿਗਨਲ ਲਈ ਸਭ ਤੋਂ ਨਜ਼ਦੀਕੀ ਲੂਪ ਪ੍ਰਦਾਨ ਕਰਨ ਲਈ ਸਿਗਨਲ ਤਬਦੀਲੀ ਦੇ ਥਰੋ-ਹੋਲ ਦੇ ਨੇੜੇ ਕੁਝ ਜ਼ਮੀਨੀ ਥਰੋ-ਹੋਲ ਰੱਖੋ। ਤੁਸੀਂ PCB ਬੋਰਡ 'ਤੇ ਕੁਝ ਵਾਧੂ ਜ਼ਮੀਨੀ ਛੇਕ ਵੀ ਰੱਖ ਸਕਦੇ ਹੋ।

ਉੱਚ ਘਣਤਾ ਵਾਲੇ ਹਾਈ ਸਪੀਡ ਪੀਸੀਬੀ ਬੋਰਡਾਂ ਲਈ, ਤੁਸੀਂ ਮਾਈਕ੍ਰੋ-ਹੋਲ ਦੀ ਵਰਤੋਂ ਕਰਨ 'ਤੇ ਵਿਚਾਰ ਕਰ ਸਕਦੇ ਹੋ।