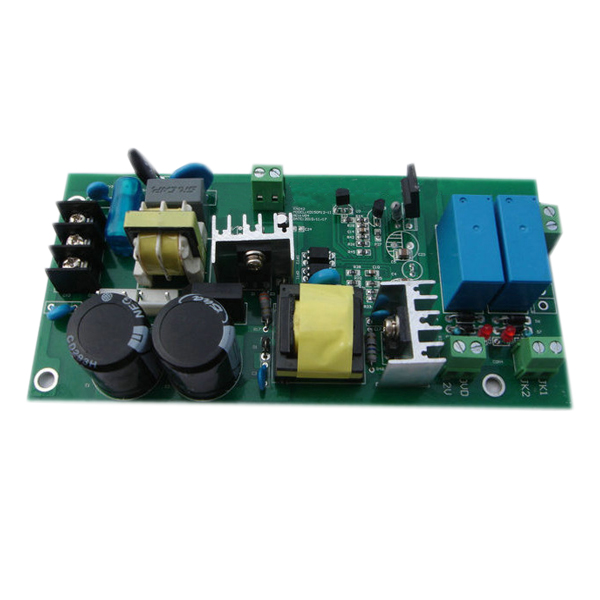

को आधारभूत प्रक्रियाPcb सर्किट बोर्डSMT चिप प्रोसेसिंगमा डिजाईन विशेष ध्यान आवश्यक छ। क्षेत्रीय योजनाबद्ध डिजाइन को एक मुख्य उद्देश्य pcb सर्किट बोर्ड डिजाइन को लागी एक नेटवर्क तालिका प्रदान गर्न र पीसीबी बोर्ड डिजाइन को लागी आधार तयार गर्न हो। बहु-लेब पासी सर्किट बोर्डको डिजाईन प्रक्रिया सामान्यतया साधारण pcb बोर्डको डिजाइन चरणहरू समान रूपमा हो। भिन्नता यो हो कि मध्यवर्ती संकेत तहको तार र आन्तरिक विद्युत तहको विभाजन गर्नु आवश्यक छ। सँगै लगियो, बहु-तह पीसीबी सर्किट बोर्डको डिजाईन मूलतः उस्तै छ। निम्न चरणहरूमा विभाजित:

1 सर्किट बोर्ड बोर्डेन योजनामा मुख्य रूपमा पीसीबी बोर्डको भौतिक आकारको योजनामा समावेश गर्दछ, कम्पोनेन्ट स्थापना विधि, र बोर्ड स्टर्डिहरू, र मुद्रा बोर्डहरू, एकल स्तरमा बोर्डहरू।

2 कार्कीटर सेटिंग, मुख्यतया काम गर्ने वातावरण प्यारामिटर सेटिंग र काम गर्ने तह प्यारामिटर सेटिंगलाई जनाउँछ। PCB वातावरण प्यारामिटरहरूको सहि र व्यावहारिक सेटिंगले सर्किट बोर्ड डिजाइनमा ठूलो सुविधा ल्याउन सक्छ र कार्य दक्षता सुधार गर्दछ।

3। कम्पोनेन्ट लेआउट र समायोजन। प्रारम्भिक काम समाप्त भएपछि, नेटवर्क तालिका पीसीबीमा आयात गर्न सकिन्छ, वा नेटवर्क तालिका pCB अपडेट गरेर स्काम्बिक रेखाचित्रमा आयात गर्न सकिन्छ। कम्पोनेन्ट लेआउट र समायोजन PCB डिजाइनमा तुलनात्मक रूपमा महत्त्वपूर्ण कार्यहरू हुन्, जसले पहिले तालिमिंग र आन्तरिक विद्युतीय तहको विभाजनलाई प्रत्यक्ष असर गर्दछ।

। वाइरिंग नियम सेटिंग्स मुख्यतया चक्कर लग, जस्तै तार चौडाई, तारर र प्याड को माध्यम, र आकार को माध्यम बाट सुरक्षा दूरी को लागी। जे भए पनि वाइरिंग विधि अपनाईएको छ, वाइरिंग नियमहरू आवश्यक छन्। एक अपरिहार्य कदम, राम्रो तारा नियमहरूले प्रोजेक्टर्ड बोर्डर मार्गको सुरक्षा सुनिश्चित गर्न, र लागत बचत गर्न सक्दछ।

Bible अन्य सहायक अपरेसनहरू, जस्तै तामा कोटिंग र Toardroploply भरिने, साथै कागजात प्रोसेसिंग जस्तै रिपोर्ट आउटपुट र मुद्रण बचत गर्नुहोस्। यी फाईलहरू PCB सर्किट बोर्डहरू जाँच गर्न र परिमार्जन गर्न प्रयोग गर्न सकिन्छ, र खरीद गरिएको कम्पोनेन्टहरूको सूची पनि प्रयोग गर्न सकिन्छ।

कम्पोनेन्ट मार्ग नियमहरू

1 क्षेत्र भित्र कुनै तारिखमा छैन ≤1mm बाट PCB बोर्डबाट र माउन्टिंग प्वालको वरिपरि 1 मिमी भित्र अनुमति छैन;

2 सत्ता रेखा सकेसम्म फराकिलो हुनुपर्दछ र 1 18 मिल भन्दा कम हुनु हुँदैन; सिग्नल लाइन चौड़ाई 12 मिली भन्दा कम हुनु हुँदैन; CPU इनपुट र आउटपुट लाइनहरू 10 मिली (वा 8 मिली) भन्दा कम हुनु हुँदैन; रेखा स्पेसिंग 10 मिली भन्दा कम हुनु हुँदैन;

।

। दोहोरो इन-लाइन प्लग: प्याड 600 मिलिमिल, Aprtare 40mil; 1 / 4ww प्रतिरोधक: 51 * * 55 55 माइल (0808005 सतह माउन्ट); जब प्लग इन, प्याड 622mil, एपर्चर 42mil; इलेक्ट्रोभेडस्टास कर्भर: * 1 * 55 55 माइल (080805 सतह माउन्ट); सिधा सम्मिलित गर्दा, प्याड 50mil र प्वाल व्यास 2 28 मिली हो;

Ly। सत्ता लाइनर र जमिन तारहरू सकेसम्म रेडियल हुनुपर्दछ, र संकेत लाइनहरु माथि माउन्ट गर्न हुँदैन।