via बहु-तह पीसीबी को एक महत्वपूर्ण घटक हो, र ड्रिलिंग को लागत सामान्यतया PCB बोर्ड को लागत को 30% देखि 40% को लागी खाता हो। सरल शब्दमा भन्नुपर्दा, PCB मा प्रत्येक प्वाललाई via भनिन्छ।

मार्फत को आधारभूत अवधारणा:

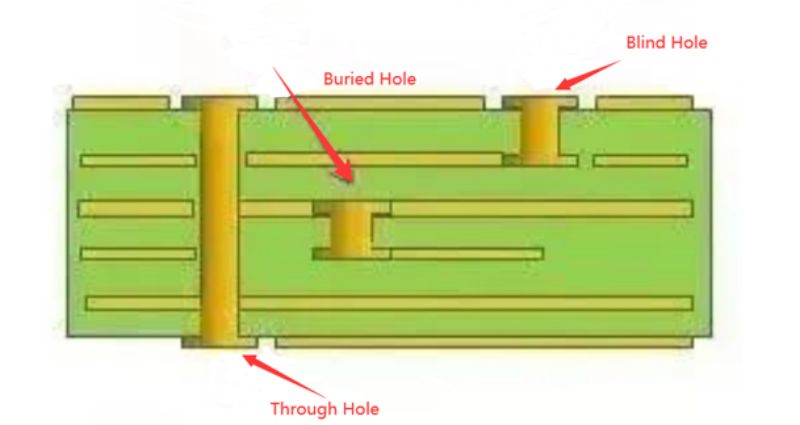

प्रकार्यको दृष्टिकोणबाट, via लाई दुई कोटीहरूमा विभाजन गर्न सकिन्छ: एउटा तहहरू बीचको विद्युतीय जडानको रूपमा प्रयोग गरिन्छ, र अर्कोलाई उपकरणको फिक्सिङ वा स्थितिको रूपमा प्रयोग गरिन्छ। यदि प्रक्रियाबाट, यी प्वालहरू सामान्यतया तीन कोटीहरूमा विभाजित हुन्छन्, अर्थात् अन्धा प्वालहरू, गाडिएका प्वालहरू र प्वालहरूद्वारा।

ब्लाइन्ड प्वालहरू छापिएको सर्किट बोर्डको माथि र तल्लो सतहहरूमा अवस्थित हुन्छन् र सतह सर्किट र तलको भित्री सर्किटको जडानको लागि निश्चित गहिराइ हुन्छ, र प्वालहरूको गहिराई सामान्यतया एक निश्चित अनुपात (एपर्चर) भन्दा बढी हुँदैन।

दफन गरिएको प्वालले मुद्रित सर्किट बोर्डको भित्री तहमा अवस्थित जडान प्वाललाई बुझाउँछ, जुन बोर्डको सतहमा विस्तार हुँदैन। माथिका दुई प्रकारका प्वालहरू सर्किट बोर्डको भित्री तहमा अवस्थित हुन्छन्, जुन ल्यामिनेशन अघि थ्रु होल मोल्डिङ प्रक्रियाद्वारा पूरा हुन्छ, र प्वाल बनाउँदा धेरै भित्री तहहरू ओभरल्याप हुन सक्छन्।

तेस्रो प्रकारलाई थ्रु-होल भनिन्छ, जुन सम्पूर्ण सर्किट बोर्डबाट जान्छ र आन्तरिक अन्तरसम्बन्ध प्राप्त गर्न वा कम्पोनेन्टहरूका लागि स्थापना स्थिति प्वालहरूको रूपमा प्रयोग गर्न सकिन्छ। किनभने प्वाल मार्फत प्रक्रियामा प्राप्त गर्न सजिलो छ र लागत कम छ, मुद्रित सर्किट बोर्डहरूको विशाल बहुमतले यसलाई प्रयोग गर्दछ, अन्य दुई प्वालहरू मार्फत भन्दा। निम्न प्वालहरू, विशेष निर्देशनहरू बिना, प्वालहरू मार्फत मानिन्छ।

डिजाइनको दृष्टिकोणबाट, ए via मुख्यतया दुई भागहरू मिलेर बनेको हुन्छ, एउटा ड्रिलिंग प्वालको बीचमा हुन्छ, र अर्को ड्रिलिंग प्वालको वरिपरि वेल्डिङ प्याड क्षेत्र हो। यी दुई भागहरूको आकार via को आकार निर्धारण गर्दछ।

स्पष्ट रूपमा, उच्च-गति, उच्च-घनत्व PCB डिजाइनमा, डिजाइनरहरू सधैं सकेसम्म सानो प्वाल चाहन्छन्, ताकि थप तारिङ ठाउँ छोड्न सकोस्, थप रूपमा, मार्फत सानो, यसको आफ्नै परजीवी क्षमता सानो, अधिक उपयुक्त छ। उच्च गति सर्किट को लागी।

यद्यपि, मार्फत साइजको कमीले लागतमा वृद्धि पनि ल्याउँछ, र प्वालको आकार अनिश्चित रूपमा घटाउन सकिँदैन, यो ड्रिलिंग र इलेक्ट्रोप्लेटिंग प्रविधिद्वारा सीमित छ: प्वाल जति सानो हुन्छ, ड्रिलिंगले जति लामो समय लिन्छ, त्यति नै सजिलो हुन्छ। केन्द्रबाट विचलित हुनु हो; जब प्वालको गहिराई प्वालको व्यास भन्दा 6 गुणा बढी हुन्छ, यो सुनिश्चित गर्न असम्भव छ कि प्वालको पर्खालमा तामाले समान रूपमा प्लेटेड गर्न सकिन्छ।

उदाहरण को लागी, यदि सामान्य 6-तह PCB बोर्ड को मोटाई (प्वाल गहिराई मार्फत) 50Mil छ, तब PCB निर्माताहरूले सामान्य अवस्थामा प्रदान गर्न सक्ने न्यूनतम ड्रिलिंग व्यास मात्र 8Mil पुग्न सक्छ। लेजर ड्रिलिंग टेक्नोलोजीको विकासको साथ, ड्रिलिंगको आकार पनि सानो र सानो हुन सक्छ, र प्वालको व्यास सामान्यतया 6Mils भन्दा कम वा बराबर हुन्छ, हामीलाई माइक्रोहोल भनिन्छ।

माइक्रोहोलहरू प्रायः एचडीआई (उच्च घनत्व इन्टरकनेक्ट संरचना) डिजाइनमा प्रयोग गरिन्छ, र माइक्रोहोल टेक्नोलोजीले प्वाललाई सीधै प्याडमा ड्रिल गर्न अनुमति दिन्छ, जसले सर्किट कार्यसम्पादनमा ठूलो सुधार गर्छ र तारिङ ठाउँ बचत गर्छ। via प्रसारण लाइनमा प्रतिबाधा विच्छेदको ब्रेकपोइन्टको रूपमा देखिन्छ, जसले संकेतको प्रतिबिम्ब बनाउँछ। सामान्यतया, प्वालको बराबर प्रतिबाधा ट्रान्समिशन लाइन भन्दा लगभग 12% कम हुन्छ, उदाहरणका लागि, 50 ohms प्रसारण लाइनको प्रतिबाधा 6 ohms द्वारा घटाइनेछ जब यो प्वालबाट गुज्र्छ (विशेष गरी र मार्फत को आकार, प्लेट मोटाई पनि सम्बन्धित छ, पूर्ण कमी होइन)।

यद्यपि, प्रतिबाधा विच्छेदन मार्फत हुने प्रतिबिम्ब वास्तवमा धेरै सानो छ, र यसको प्रतिबिम्ब गुणांक मात्र हो:

(४४-५०)/(४४ + ५०) = ०.०६

माध्यमबाट उत्पन्न हुने समस्याहरू परजीवी क्यापेसिटन्स र इन्डक्टन्सको प्रभावहरूमा बढी केन्द्रित छन्।

Via's Parasitic Capacitance र Inductance

त्यहाँ आफैंमा परजीवी आवारा क्षमता छ। यदि राखिएको तहमा सोल्डर प्रतिरोध क्षेत्रको व्यास D2 हो, सोल्डर प्याडको व्यास D1 हो, PCB बोर्डको मोटाई T हो, र सब्सट्रेटको डाइलेक्ट्रिक स्थिरता ε हो, प्वालको माध्यमबाट परजीवी क्यापेसिटन्स। लगभग छ:

C=1.41εTD1/(D2-D1)

सर्किटमा परजीवी क्यापेसिटन्सको मुख्य प्रभाव भनेको संकेतको वृद्धि समयलाई लम्ब्याउनु र सर्किटको गति कम गर्नु हो।

उदाहरण को लागी, 50Mil को मोटाई संग PCB को लागी, यदि via pad को व्यास 20Mil (ड्रिलिंग प्वाल को व्यास 10Mil छ) र सोल्डर प्रतिरोध क्षेत्र को व्यास 40Mil छ, तब हामी परजीवी क्षमता को अनुमानित गर्न सक्छौं। माथिको सूत्र द्वारा मार्फत:

C=1.41x4.4x0.050x0.020/(0.040-0.020)=0.31pF

क्षमता को यो भाग को कारण वृद्धि समय परिवर्तन को मात्रा लगभग छ:

T10-90=2.2C(Z0/2)=2.2x0.31x(50/2)=17.05ps

यी मानहरूबाट यो देख्न सकिन्छ कि एकल via को परजीवी क्यापेसिटन्सले गर्दा हुने वृद्धि ढिलाइको उपयोगिता धेरै स्पष्ट छैन, यदि via लाई तहहरू बीच स्विच गर्न लाइनमा धेरै पटक प्रयोग गरिन्छ भने, धेरै प्वालहरू प्रयोग हुनेछन्, र डिजाइन ध्यानपूर्वक विचार गर्नुपर्छ। वास्तविक डिजाइनमा, प्वाल र तामाको क्षेत्र (एन्टि-प्याड) बीचको दूरी बढाएर वा प्याडको व्यास घटाएर परजीवी क्यापेसिटन्स घटाउन सकिन्छ।

हाई-स्पीड डिजिटल सर्किटहरूको डिजाइनमा, परजीवी इन्डक्टन्सले गर्दा हुने हानि प्रायः परजीवी क्यापेसिटन्सको प्रभावभन्दा बढी हुन्छ। यसको परजीवी श्रृंखला इन्डक्टन्सले बाइपास क्यापेसिटरको योगदानलाई कमजोर पार्छ र सम्पूर्ण पावर प्रणालीको फिल्टरिंग प्रभावकारितालाई कमजोर बनाउँछ।

हामी निम्न अनुभवजन्य सूत्र प्रयोग गर्न सक्छौं केवल थ्रु-होल अनुमानको परजीवी इन्डक्टन्स गणना गर्न:

L=5.08h[ln(4h/d)+1]

जहाँ L ले via को inductance लाई जनाउँछ, h via को लम्बाइ हो, र d केन्द्रीय प्वालको व्यास हो। यो सूत्रबाट देख्न सकिन्छ कि via को व्यास inductance मा कम प्रभाव छ, जबकि via को लम्बाई inductance मा सबैभन्दा ठूलो प्रभाव छ। अझै पनि माथिको उदाहरण प्रयोग गरेर, आउट-अफ-होल इन्डक्टन्स यस रूपमा गणना गर्न सकिन्छ:

L=5.08x0.050[ln(4x0.050/0.010)+1]=1.015nH

यदि संकेतको वृद्धि समय 1ns हो, त्यसपछि यसको बराबर प्रतिबाधा आकार हो:

XL=πL/T10-90=3.19Ω

यस्तो प्रतिबाधा मार्फत उच्च आवृत्ति वर्तमान को उपस्थिति मा बेवास्ता गर्न सकिदैन, विशेष गरी, ध्यान दिनुहोस् कि बाईपास क्यापेसिटर पावर तह र गठन जडान गर्दा दुई प्वालहरु मा पास गर्न आवश्यक छ, ताकि प्वाल को परजीवी inductance गुणन हुनेछ।

मार्फत कसरी प्रयोग गर्ने?

प्वालको परजीवी विशेषताहरूको माथिको विश्लेषणको माध्यमबाट, हामी देख्न सक्छौं कि उच्च-गति PCB डिजाइनमा, साधारण देखिने प्वालहरूले सर्किटको डिजाइनमा धेरै नकारात्मक प्रभावहरू ल्याउँछ। प्वालको परजीवी प्रभावले गर्दा हुने प्रतिकूल प्रभावहरूलाई कम गर्नको लागि, डिजाइन सम्भव भएसम्म हुन सक्छ:

लागत र सिग्नल गुणस्तरका दुई पक्षहरूबाट, मार्फत साइजको उचित आकार छान्नुहोस्। आवश्यक भएमा, तपाईले बिजुली आपूर्ति वा ग्राउन्ड तार प्वालहरू जस्ता विभिन्न साइजको भियाहरू प्रयोग गर्ने बारे विचार गर्न सक्नुहुन्छ, प्रतिबाधा कम गर्नको लागि तपाईले ठूलो साइज प्रयोग गर्न विचार गर्न सक्नुहुन्छ, र सिग्नल तारहरूको लागि, तपाईले सानो माध्यम प्रयोग गर्न सक्नुहुन्छ। अवश्य पनि, via को आकार घट्दै जाँदा, सम्बन्धित लागत पनि बढ्नेछ

माथि छलफल गरिएका दुई सूत्रहरू निष्कर्षमा पुग्न सकिन्छ कि पातलो पीसीबी बोर्डको प्रयोग दुई परजीवी मापदण्डहरू कम गर्न अनुकूल छ।

PCB बोर्डमा सिग्नल तारहरू सकेसम्म परिवर्तन गर्नु हुँदैन, अर्थात्, अनावश्यक वियास प्रयोग नगर्ने प्रयास गर्नुहोस्।

वियासलाई पावर सप्लाईको पिन र जमिनमा ड्रिल गरिनुपर्छ। पिन र वियास बीचको सिसा जति छोटो हुन्छ, त्यति राम्रो। धेरै प्वालहरू समानान्तरमा ड्रिल गर्न सकिन्छ समान इन्डक्टन्स कम गर्न।

सिग्नलको लागि नजिकको लूप प्रदान गर्न सिग्नल परिवर्तनको थ्रु-होल नजिक केही ग्राउन्ड गरिएको थ्रु-होलहरू राख्नुहोस्। तपाइँ PCB बोर्डमा केही अतिरिक्त ग्राउन्ड प्वालहरू पनि राख्न सक्नुहुन्छ।

उच्च घनत्व संग उच्च गति PCB बोर्ड को लागी, तपाईं माइक्रो-प्वाल प्रयोग गर्न विचार गर्न सक्नुहुन्छ।