VIA adalah salah satu komponen penting PCB berbilang lapisan, dan kos penggerudian biasanya menyumbang 30% hingga 40% daripada kos papan PCB. Ringkasnya, setiap lubang pada PCB boleh dipanggil melalui.

Konsep Asas Via:

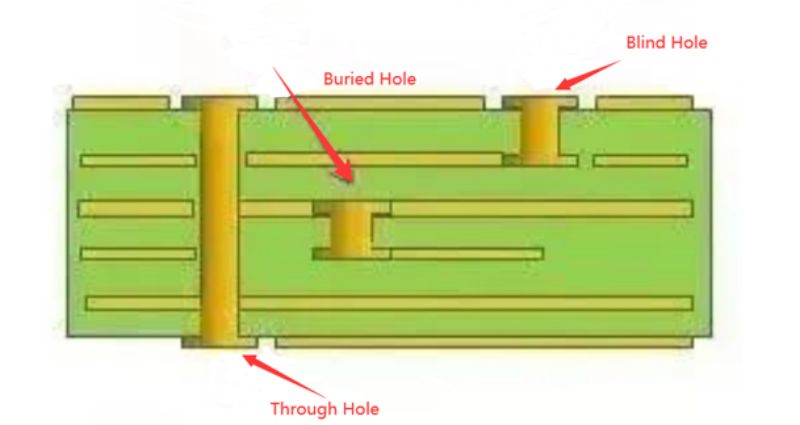

Dari sudut pandangan fungsi, VI boleh dibahagikan kepada dua kategori: satu digunakan sebagai sambungan elektrik antara lapisan, dan yang lain digunakan sebagai penetapan atau kedudukan peranti. Jika dari proses, lubang -lubang ini secara amnya dibahagikan kepada tiga kategori, iaitu lubang buta, lubang terkubur dan melalui lubang.

Lubang -lubang buta terletak di permukaan atas dan bawah papan litar bercetak dan mempunyai kedalaman tertentu untuk sambungan litar permukaan dan litar dalaman di bawah, dan kedalaman lubang biasanya tidak melebihi nisbah tertentu (aperture).

Lubang yang dikebumikan merujuk kepada lubang sambungan yang terletak di lapisan dalaman papan litar bercetak, yang tidak dilanjutkan ke permukaan papan. Dua jenis lubang di atas terletak di lapisan dalaman papan litar, yang disiapkan oleh proses pencetakan melalui lubang sebelum laminasi, dan beberapa lapisan dalaman mungkin bertindih semasa pembentukan lubang melalui.

Jenis ketiga dipanggil melalui lubang, yang melalui seluruh papan litar dan boleh digunakan untuk mencapai interkoneksi dalaman atau sebagai lubang kedudukan pemasangan untuk komponen. Kerana melalui lubang lebih mudah dicapai dalam proses dan kosnya lebih rendah, sebahagian besar papan litar bercetak menggunakannya, bukannya dua lagi melalui lubang. Lubang -lubang berikut, tanpa arahan khas, dianggap sebagai melalui lubang.

Dari sudut pandangan reka bentuk, A VIA terutamanya terdiri daripada dua bahagian, satu adalah tengah lubang penggerudian, dan yang lain adalah kawasan pad kimpalan di sekitar lubang penggerudian. Saiz kedua -dua bahagian ini menentukan saiz VIA.

Jelas sekali, dalam reka bentuk PCB berkepadatan tinggi, pereka, pereka sentiasa menginginkan lubang sekecil mungkin, supaya lebih banyak ruang pendawaian dapat ditinggalkan, di samping itu, lebih kecil daripada, kapasitans parasitnya sendiri lebih kecil, lebih sesuai untuk litar berkelajuan tinggi.

Walau bagaimanapun, pengurangan saiz VIA juga membawa peningkatan kos, dan saiz lubang tidak dapat dikurangkan selama -lamanya, ia dibatasi oleh teknologi penggerudian dan elektroplating: semakin kecil lubang, semakin lama penggerudian mengambil, lebih mudah untuk menyimpang dari pusat; Apabila kedalaman lubang lebih dari 6 kali diameter lubang, adalah mustahil untuk memastikan dinding lubang dapat disalurkan secara seragam dengan tembaga.

Sebagai contoh, jika ketebalan (melalui kedalaman lubang) papan PCB 6-lapisan biasa adalah 50 juta, maka diameter penggerudian minimum yang boleh disediakan oleh pengeluar PCB di bawah keadaan normal hanya boleh mencapai 8 juta. Dengan perkembangan teknologi penggerudian laser, saiz penggerudian juga boleh menjadi lebih kecil dan lebih kecil, dan diameter lubang pada umumnya kurang daripada atau sama dengan 6mils, kami dipanggil mikro.

Mikrolus sering digunakan dalam reka bentuk HDI (struktur kepadatan tinggi), dan teknologi mikrohole boleh membolehkan lubang terus dibor pada pad, yang sangat meningkatkan prestasi litar dan menjimatkan ruang pendawaian. VIA muncul sebagai titik putus keterukan impedans pada talian penghantaran, menyebabkan refleksi isyarat. Secara amnya, impedans setara lubang adalah kira -kira 12% lebih rendah daripada garis penghantaran, contohnya, impedans garisan penghantaran 50 ohms akan dikurangkan sebanyak 6 ohms apabila ia melalui lubang (khusus dan saiz VIA, ketebalan plat juga berkaitan, bukan pengurangan mutlak).

Walau bagaimanapun, refleksi yang disebabkan oleh ketidakpastian impedans melalui sebenarnya sangat kecil, dan pekali pantulannya hanya:

(44-50)/(44 + 50) = 0.06

Masalah yang timbul dari Via lebih tertumpu pada kesan kapasitans parasit dan induktansi.

Kapasiti dan induktansi Parasit Via

Terdapat kapasitansi liar parasit di Via itu sendiri. Jika diameter zon rintangan solder pada lapisan santai adalah D2, diameter pad solder adalah D1, ketebalan papan PCB adalah T, dan pemalar dielektrik substrat adalah ε, kapasitans parasit melalui lubang melalui lubang adalah kira -kira:

C = 1.41εTD1/(D2-D1)

Kesan utama kapasitans parasit pada litar adalah untuk memanjangkan masa peningkatan isyarat dan mengurangkan kelajuan litar.

Sebagai contoh, untuk PCB dengan ketebalan 50 juta, jika diameter pad Via adalah 20 juta (diameter lubang penggerudian adalah 10mils) dan diameter zon rintangan solder adalah 40 juta, maka kita boleh menghampiri kapasitans parasit VIA oleh formula di atas:

C = 1.41x4.4x0.050x0.020/(0.040-0.020) = 0.31pf

Jumlah perubahan masa kenaikan yang disebabkan oleh bahagian kapasitansi ini adalah kira -kira:

T10-90 = 2.2C (Z0/2) = 2.2x0.31x (50/2) = 17.05ps

Ia dapat dilihat dari nilai -nilai ini bahawa walaupun utiliti kelewatan kenaikan yang disebabkan oleh kapasitans parasit satu VIA tidak begitu jelas, jika VIA digunakan beberapa kali dalam baris untuk beralih antara lapisan, banyak lubang akan digunakan, dan reka bentuk harus dipertimbangkan dengan teliti. Dalam reka bentuk sebenar, kapasitans parasit dapat dikurangkan dengan meningkatkan jarak antara lubang dan kawasan tembaga (anti-pad) atau mengurangkan diameter pad.

Dalam reka bentuk litar digital berkelajuan tinggi, kemudaratan yang disebabkan oleh induktansi parasit sering lebih besar daripada pengaruh kapasitans parasit. Induktansi siri parasitnya akan melemahkan sumbangan kapasitor pintasan dan melemahkan keberkesanan penapisan sistem kuasa keseluruhan.

Kita boleh menggunakan formula empirikal berikut untuk mengira induktansi parasit penghampiran melalui lubang:

L = 5.08H [LN (4H/D) +1]

Di mana L merujuk kepada induktansi VIA, H ialah panjang VIA, dan D adalah diameter lubang pusat. Ia dapat dilihat dari formula bahawa diameter VIA mempunyai sedikit pengaruh terhadap induktansi, sementara panjang VIA mempunyai pengaruh terbesar terhadap induktansi. Masih menggunakan contoh di atas, induktansi luar lubang boleh dikira sebagai:

L = 5.08x0.050 [LN (4x0.050/0.010) +1] = 1.015NH

Jika masa kenaikan isyarat adalah 1Ns, maka saiz impedans yang setara ialah:

Xl = πl/t10-90 = 3.19Ω

Impedans tersebut tidak boleh diabaikan dengan kehadiran arus frekuensi tinggi melalui, khususnya, ambil perhatian bahawa kapasitor pintasan perlu melalui dua lubang apabila menyambungkan lapisan kuasa dan pembentukan, supaya induktansi parasit lubang akan didarab.

Bagaimana cara menggunakan melalui?

Melalui analisis di atas ciri-ciri parasit lubang, kita dapat melihat bahawa dalam reka bentuk PCB berkelajuan tinggi, lubang-lubang yang seolah-olah mudah sering membawa kesan negatif yang besar kepada reka bentuk litar. Untuk mengurangkan kesan buruk yang disebabkan oleh kesan parasit lubang, reka bentuk boleh sejauh mungkin:

Dari dua aspek kos dan kualiti isyarat, pilih saiz yang munasabah dari saiz melalui. Sekiranya perlu, anda boleh mempertimbangkan menggunakan saiz vias yang berbeza, seperti untuk bekalan kuasa atau lubang dawai tanah, anda boleh mempertimbangkan menggunakan saiz yang lebih besar untuk mengurangkan impedans, dan untuk pendawaian isyarat, anda boleh menggunakan lebih kecil melalui. Sudah tentu, kerana saiz VIA berkurangan, kos yang sepadan juga akan meningkat

Kedua -dua formula yang dibincangkan di atas dapat disimpulkan bahawa penggunaan papan PCB yang lebih nipis adalah kondusif untuk mengurangkan dua parameter parasit di Via

Pendawaian isyarat pada papan PCB tidak boleh diubah sejauh mungkin, iaitu, cuba untuk tidak menggunakan vias yang tidak perlu.

Vias mesti digerudi ke dalam pin bekalan kuasa dan tanah. Lebih pendek memimpin antara pin dan vias, lebih baik. Lubang berbilang boleh digerudi selari untuk mengurangkan induktansi setara.

Letakkan beberapa lubang melalui lubang berhampiran lubang-lubang perubahan isyarat untuk menyediakan gelung terdekat untuk isyarat. Anda juga boleh meletakkan beberapa lubang tanah yang berlebihan di papan PCB.

Untuk papan PCB berkelajuan tinggi dengan ketumpatan tinggi, anda boleh mempertimbangkan menggunakan lubang mikro.