पीसीबी लेआउट आणि वायरिंगच्या समस्येबद्दल, आज आपण सिग्नल इंटिग्रिटी ॲनालिसिस (SI), इलेक्ट्रोमॅग्नेटिक कंपॅटिबिलिटी ॲनालिसिस (EMC), पॉवर इंटिग्रिटी ॲनालिसिस (PI) बद्दल बोलणार नाही. केवळ मॅन्युफॅक्चरिबिलिटी ॲनालिसिस (DFM) बद्दल बोलणे, मॅन्युफॅक्चरिबिलिटीच्या अवास्तव डिझाइनमुळे देखील उत्पादनाची रचना अपयशी ठरेल.

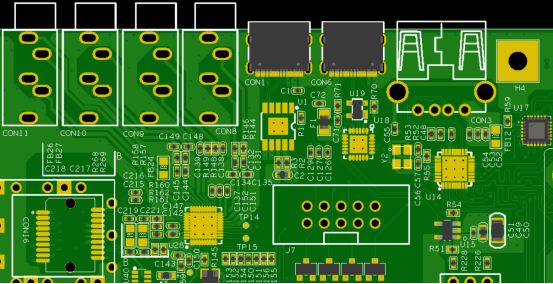

PCB लेआउटमधील यशस्वी DFM महत्त्वाच्या DFM अडचणींसाठी डिझाइन नियम सेट करण्यापासून सुरू होते. खाली दर्शविलेले DFM नियम काही समकालीन डिझाइन क्षमता दर्शवतात ज्या बहुतेक उत्पादक शोधू शकतात. PCB डिझाइन नियमांमध्ये सेट केलेल्या मर्यादांचे उल्लंघन होत नाही याची खात्री करा जेणेकरून बहुतेक मानक डिझाइन निर्बंध सुनिश्चित केले जाऊ शकतात.

PCB राउटिंगची DFM समस्या चांगल्या PCB मांडणीवर अवलंबून असते, आणि राउटिंगचे नियम प्रीसेट केले जाऊ शकतात, ज्यामध्ये रेषेच्या वाकण्याच्या वेळेची संख्या, वहन होलची संख्या, पायऱ्यांची संख्या इ. साधारणपणे, एक्सप्लोरेटरी वायरिंग चालते. लहान रेषा पटकन जोडण्यासाठी प्रथम बाहेर पडा, आणि नंतर चक्रव्यूह वायरिंग चालते. ग्लोबल राउटिंग पाथ ऑप्टिमायझेशन प्रथम ठेवल्या जाणाऱ्या तारांवर केले जाते आणि संपूर्ण प्रभाव आणि DFM उत्पादनक्षमता सुधारण्यासाठी री-वायरिंगचा प्रयत्न केला जातो.

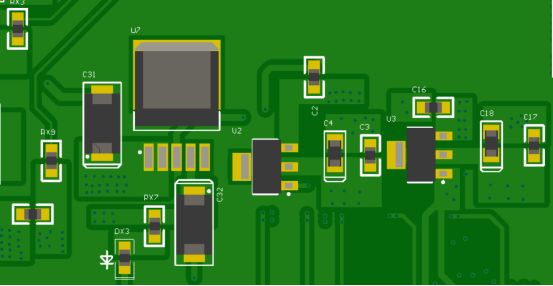

1.SMT उपकरणे

डिव्हाइस लेआउट स्पेसिंग असेंबली आवश्यकता पूर्ण करते, आणि साधारणपणे पृष्ठभाग माउंट केलेल्या उपकरणांसाठी 20mil पेक्षा जास्त, IC उपकरणांसाठी 80mil आणि BGA उपकरणांसाठी 200mi. उत्पादन प्रक्रियेची गुणवत्ता आणि उत्पन्न सुधारण्यासाठी, डिव्हाइस अंतर विधानसभा आवश्यकता पूर्ण करू शकते.

साधारणपणे, डिव्हाइस पिनच्या SMD पॅडमधील अंतर 6mil पेक्षा जास्त असावे आणि सोल्डर सोल्डर ब्रिजची फॅब्रिकेशन क्षमता 4mil आहे. जर SMD पॅडमधील अंतर 6mil पेक्षा कमी असेल आणि सोल्डर विंडोमधील अंतर 4mil पेक्षा कमी असेल, तर सोल्डर ब्रिज टिकवून ठेवता येत नाही, परिणामी असेंबली प्रक्रियेत सोल्डरचे मोठे तुकडे (विशेषतः पिन दरम्यान) तयार होतात, ज्यामुळे शॉर्ट सर्किट करण्यासाठी.

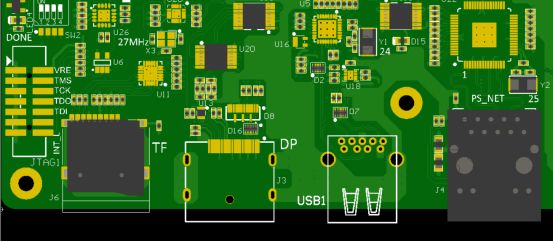

2.DIP डिव्हाइस

ओव्हर वेव्ह सोल्डरिंग प्रक्रियेतील उपकरणांचे पिन अंतर, दिशा आणि अंतर लक्षात घेतले पाहिजे. डिव्हाइसच्या अपुरा पिन अंतरामुळे सोल्डरिंग टिन होईल, ज्यामुळे शॉर्ट सर्किट होईल.

बरेच डिझाइनर इन-लाइन डिव्हाइसेस (THTS) चा वापर कमी करतात किंवा त्यांना बोर्डच्या त्याच बाजूला ठेवतात. तथापि, इन-लाइन उपकरणे अनेकदा अपरिहार्य असतात. संयोजनाच्या बाबतीत, जर इन-लाइन डिव्हाइस शीर्ष स्तरावर ठेवले असेल आणि पॅच डिव्हाइस खालच्या स्तरावर ठेवले असेल, तर काही प्रकरणांमध्ये, ते सिंगल-साइड वेव्ह सोल्डरिंगवर परिणाम करेल. या प्रकरणात, अधिक महाग वेल्डिंग प्रक्रिया, जसे की निवडक वेल्डिंग, वापरल्या जातात.

3. घटक आणि प्लेटच्या काठातील अंतर

जर ते मशीन वेल्डिंग असेल तर, इलेक्ट्रॉनिक घटक आणि बोर्डच्या काठातील अंतर साधारणपणे 7 मिमी असते (वेगवेगळ्या वेल्डिंग उत्पादकांच्या वेगवेगळ्या आवश्यकता असतात), परंतु ते पीसीबी उत्पादन प्रक्रियेच्या काठामध्ये देखील जोडले जाऊ शकते, जेणेकरून इलेक्ट्रॉनिक घटक जोपर्यंत ते वायरिंगसाठी सोयीचे असेल तोपर्यंत पीसीबी बोर्डच्या काठावर ठेवले जाते.

तथापि, जेव्हा प्लेटच्या काठाला वेल्डेड केले जाते, तेव्हा ते मशीनच्या मार्गदर्शक रेलचा सामना करू शकते आणि घटकांचे नुकसान करू शकते. प्लेटच्या काठावर असलेले डिव्हाइस पॅड उत्पादन प्रक्रियेत काढले जाईल. पॅड लहान असल्यास, वेल्डिंग गुणवत्ता प्रभावित होईल.

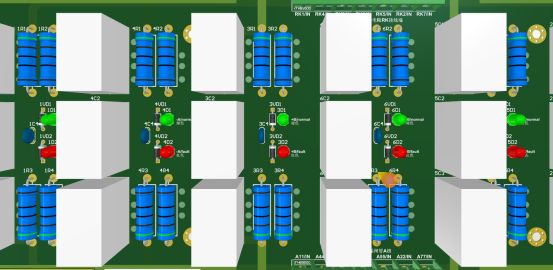

4.उच्च/निम्न उपकरणांचे अंतर

अनेक प्रकारचे इलेक्ट्रॉनिक घटक, वेगवेगळे आकार आणि विविध प्रकारच्या लीड लाइन्स आहेत, त्यामुळे मुद्रित फलकांच्या असेंबली पद्धतीमध्ये फरक आहेत. चांगल्या मांडणीमुळे मशीनची कार्यक्षमता स्थिर होऊ शकते, शॉक प्रूफ होऊ शकतो, नुकसान कमी होऊ शकते, परंतु मशीनच्या आत एक व्यवस्थित आणि सुंदर प्रभाव देखील मिळू शकतो.

लहान उपकरणे उच्च उपकरणांभोवती विशिष्ट अंतरावर ठेवली पाहिजेत. डिव्हाइसच्या उंचीच्या गुणोत्तरातील डिव्हाइस अंतर लहान आहे, एक असमान थर्मल वेव्ह आहे, ज्यामुळे वेल्डिंगनंतर खराब वेल्डिंग किंवा दुरुस्तीचा धोका असू शकतो.

5.डिव्हाइस ते डिव्हाइस अंतर

सामान्य smt प्रक्रियेत, मशीनच्या माउंटिंगमधील काही त्रुटी लक्षात घेणे आणि देखभाल आणि दृश्य तपासणीची सोय लक्षात घेणे आवश्यक आहे. दोन समीप घटक खूप जवळ नसावेत आणि विशिष्ट सुरक्षित अंतर सोडले पाहिजे.

फ्लेक घटक, SOT, SOIC आणि फ्लेक घटकांमधील अंतर 1.25 मिमी आहे. फ्लेक घटक, SOT, SOIC आणि फ्लेक घटकांमधील अंतर 1.25 मिमी आहे. PLCC आणि फ्लेक घटक, SOIC आणि QFP दरम्यान 2.5 मि.मी. PLCCS दरम्यान 4 मि.मी. PLCC सॉकेट्सची रचना करताना, PLCC सॉकेटच्या आकाराची (PLCC पिन सॉकेटच्या तळाशी असते) अनुमती देण्याची काळजी घेतली पाहिजे.

6.रेषेची रुंदी/रेषा अंतर

डिझायनर्ससाठी, डिझाइनच्या प्रक्रियेत, आम्ही केवळ डिझाइनच्या आवश्यकतांची अचूकता आणि परिपूर्णता विचारात घेऊ शकत नाही, उत्पादन प्रक्रियेवर एक मोठा निर्बंध आहे. चांगल्या उत्पादनाच्या जन्मासाठी बोर्ड कारखान्यासाठी नवीन उत्पादन लाइन तयार करणे अशक्य आहे.

सामान्य परिस्थितीत, डाउन लाईनची रुंदी 4/4mil पर्यंत नियंत्रित केली जाते आणि छिद्र 8mil (0.2mm) म्हणून निवडले जाते. मूलभूतपणे, 80% पेक्षा जास्त पीसीबी उत्पादक उत्पादन करू शकतात आणि उत्पादन खर्च सर्वात कमी आहे. रेषेची किमान रुंदी आणि रेषेचे अंतर 3/3mil पर्यंत नियंत्रित केले जाऊ शकते आणि छिद्रातून 6mil (0.15mm) निवडले जाऊ शकते. मूलभूतपणे, 70% पेक्षा जास्त पीसीबी उत्पादक ते तयार करू शकतात, परंतु किंमत पहिल्या प्रकरणापेक्षा किंचित जास्त आहे, खूप जास्त नाही.

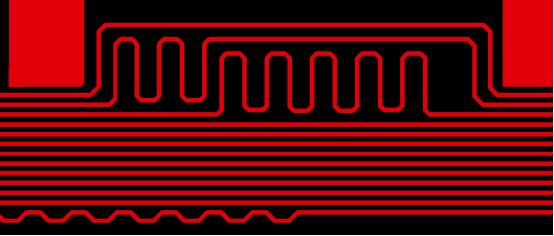

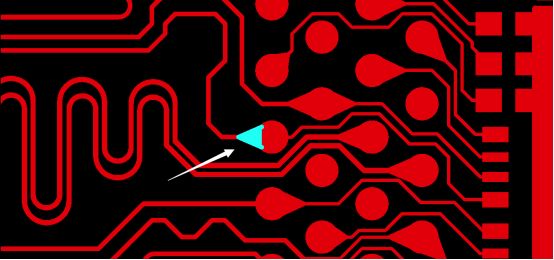

7.एक तीव्र कोन/ काटकोन

वायरिंगमध्ये शार्प अँगल रूटिंगला सामान्यतः मनाई आहे, PCB राउटिंगमध्ये परिस्थिती टाळण्यासाठी उजव्या कोन राउटिंगची आवश्यकता असते आणि वायरिंगची गुणवत्ता मोजण्यासाठी ते जवळजवळ एक मानक बनले आहे. सिग्नलच्या अखंडतेवर परिणाम झाल्यामुळे, उजव्या कोनातील वायरिंग अतिरिक्त परजीवी कॅपेसिटन्स आणि इंडक्टन्स निर्माण करेल.

PCB प्लेट बनवण्याच्या प्रक्रियेत, PCB वायर्स तीव्र कोनात एकमेकांना छेदतात, ज्यामुळे ऍसिड अँगल नावाची समस्या निर्माण होते. पीसीबी सर्किट एचिंग लिंकमध्ये, पीसीबी सर्किटचे "ॲसिड अँगल" वर जास्त गंज होईल, परिणामी पीसीबी सर्किट व्हर्च्युअल ब्रेकची समस्या उद्भवेल. म्हणून, पीसीबी अभियंत्यांनी वायरिंगमध्ये तीक्ष्ण किंवा विचित्र कोन टाळणे आवश्यक आहे आणि वायरिंगच्या कोपऱ्यात 45 अंश कोन राखणे आवश्यक आहे.

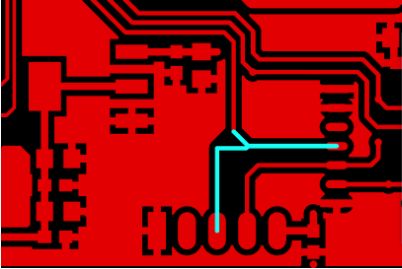

8.तांब्याची पट्टी/बेट

जर ते पुरेसे मोठे बेट तांबे असेल तर ते अँटेना बनेल, ज्यामुळे बोर्डच्या आत आवाज आणि इतर हस्तक्षेप होऊ शकतो (कारण त्याचा तांबे जमिनीवर नसतो - तो सिग्नल कलेक्टर होईल).

तांब्याच्या पट्ट्या आणि बेटे हे फ्री-फ्लोटिंग कॉपरचे अनेक सपाट स्तर आहेत, ज्यामुळे आम्ल कुंडमध्ये काही गंभीर समस्या उद्भवू शकतात. लहान तांब्याचे ठिपके पीसीबी पॅनेल तोडून पॅनेलवरील इतर खोदलेल्या भागात जाण्यासाठी ओळखले जातात, ज्यामुळे शॉर्ट सर्किट होते.

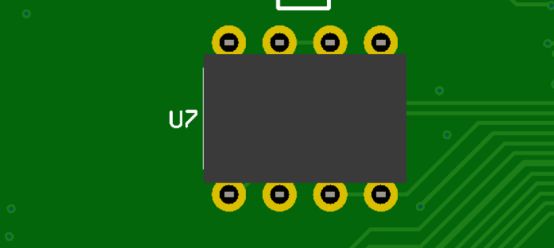

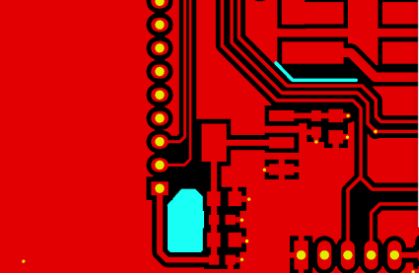

9. ड्रिलिंग होलची होल रिंग

भोक रिंग ड्रिल भोक सुमारे तांबे एक रिंग संदर्भित. उत्पादन प्रक्रियेतील सहनशीलतेमुळे, ड्रिलिंग, एचिंग आणि कॉपर प्लेटिंगनंतर, ड्रिल होलच्या सभोवतालची उरलेली तांब्याची रिंग नेहमी पॅडच्या मध्यभागी अचूकपणे आदळत नाही, ज्यामुळे भोक रिंग तुटू शकते.

होल रिंगची एक बाजू 3.5mil पेक्षा जास्त असणे आवश्यक आहे आणि प्लग-इन होल रिंग 6mil पेक्षा जास्त असणे आवश्यक आहे. भोक रिंग खूप लहान आहे. उत्पादन आणि उत्पादन प्रक्रियेत, ड्रिलिंग होलमध्ये सहिष्णुता असते आणि रेषेच्या संरेखनामध्ये देखील सहनशीलता असते. सहिष्णुतेच्या विचलनामुळे होल रिंग ओपन सर्किट तोडेल.

10. वायरिंगचे अश्रू थेंब

पीसीबी वायरिंगमध्ये अश्रू जोडणे पीसीबी बोर्डवरील सर्किट कनेक्शन अधिक स्थिर, उच्च विश्वासार्हता बनवू शकते, ज्यामुळे सिस्टम अधिक स्थिर होईल, म्हणून सर्किट बोर्डमध्ये अश्रू जोडणे आवश्यक आहे.

जेव्हा सर्किट बोर्डला मोठ्या बाह्य शक्तीचा प्रभाव पडतो तेव्हा अश्रूचे थेंब जोडल्यास वायर आणि पॅड किंवा वायर आणि पायलट होल यांच्यातील संपर्क बिंदूचे डिस्कनेक्शन टाळता येते. वेल्डिंगमध्ये अश्रूचे थेंब जोडताना, ते पॅडचे संरक्षण करू शकते, पॅड पडण्यासाठी एकाधिक वेल्डिंग टाळू शकते आणि उत्पादनादरम्यान छिद्र विक्षेपणामुळे होणारे असमान कोरीव आणि क्रॅक टाळू शकतात.