व्हिया हा मल्टी-लेयर पीसीबीचा एक महत्त्वाचा घटक आहे आणि ड्रिलिंगचा खर्च पीसीबी बोर्डच्या खर्चाच्या 30% ते 40% इतका असतो. सोप्या भाषेत सांगायचे तर PCB वरील प्रत्येक छिद्राला via असे म्हटले जाऊ शकते.

द्वारे मूलभूत संकल्पना:

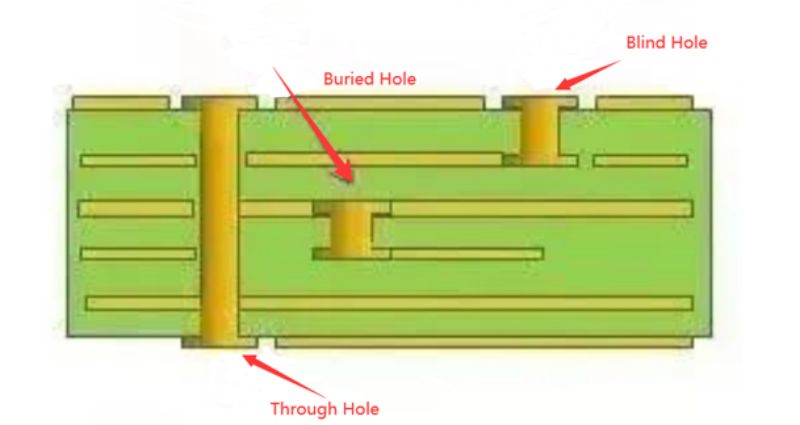

फंक्शनच्या दृष्टिकोनातून, via दोन श्रेणींमध्ये विभागले जाऊ शकते: एक थरांमधील विद्युत कनेक्शन म्हणून वापरला जातो आणि दुसरा डिव्हाइसचे निराकरण किंवा स्थिती म्हणून वापरला जातो. जर प्रक्रियेतून, ही छिद्रे सामान्यतः तीन श्रेणींमध्ये विभागली जातात, म्हणजे आंधळे छिद्र, पुरलेले छिद्र आणि छिद्रांद्वारे.

आंधळे छिद्र मुद्रित सर्किट बोर्डच्या वरच्या आणि खालच्या पृष्ठभागावर स्थित असतात आणि पृष्ठभाग सर्किट आणि खाली अंतर्गत सर्किट यांच्या कनेक्शनसाठी एक विशिष्ट खोली असते आणि छिद्रांची खोली सामान्यत: विशिष्ट गुणोत्तर (छिद्र) पेक्षा जास्त नसते.

दफन केलेले भोक हे मुद्रित सर्किट बोर्डच्या आतील स्तरामध्ये स्थित कनेक्शन होलचा संदर्भ देते, जे बोर्डच्या पृष्ठभागावर विस्तारित होत नाही. वरील दोन प्रकारची छिद्रे सर्किट बोर्डच्या आतील लेयरमध्ये असतात, जी लॅमिनेशनच्या आधी थ्रू होल मोल्डिंग प्रक्रियेद्वारे पूर्ण होते आणि थ्रू होलच्या निर्मितीदरम्यान अनेक आतील स्तर आच्छादित होऊ शकतात.

तिसऱ्या प्रकाराला थ्रू-होल म्हणतात, जे संपूर्ण सर्किट बोर्डमधून जातात आणि अंतर्गत इंटरकनेक्शन साध्य करण्यासाठी किंवा घटकांसाठी इंस्टॉलेशन पोझिशनिंग होल म्हणून वापरले जाऊ शकतात. प्रक्रियेत थ्रू होल मिळवणे सोपे असल्याने आणि खर्च कमी असल्याने, इतर दोन छिद्रांऐवजी बहुतेक मुद्रित सर्किट बोर्ड त्याचा वापर करतात. खालील छिद्र, विशेष निर्देशांशिवाय, छिद्रांद्वारे मानले जातात.

डिझाईनच्या दृष्टिकोनातून, via मुख्यत्वे दोन भागांनी बनलेला असतो, एक ड्रिलिंग होलच्या मध्यभागी असतो आणि दुसरा ड्रिलिंग होलभोवती वेल्डिंग पॅड क्षेत्र असतो. या दोन भागांचा आकार via चा आकार ठरवतो.

साहजिकच, हाय-स्पीड, हाय-डेन्सिटी पीसीबी डिझाइनमध्ये, डिझायनर्सना नेहमी छिद्र शक्य तितके लहान हवे असते, जेणेकरून वायरिंगसाठी अधिक जागा सोडता येईल, शिवाय, मार्ग जितका लहान असेल तितकी त्याची स्वतःची परजीवी क्षमता लहान, अधिक योग्य असेल. हाय-स्पीड सर्किट्ससाठी.

तथापि, द्वारे आकार कमी केल्याने खर्चातही वाढ होते आणि भोकचा आकार अनिश्चित काळासाठी कमी करता येत नाही, ते ड्रिलिंग आणि इलेक्ट्रोप्लेटिंग तंत्रज्ञानाद्वारे मर्यादित आहे: छिद्र जितके लहान असेल तितके ड्रिलिंगला जास्त वेळ लागेल. केंद्रापासून विचलित होणे आहे; जेव्हा छिद्राची खोली छिद्राच्या व्यासाच्या 6 पट जास्त असते, तेव्हा छिद्राची भिंत एकसमानपणे तांब्याने प्लेट केली जाऊ शकते याची खात्री करणे अशक्य आहे.

उदाहरणार्थ, सामान्य 6-लेयर PCB बोर्डची जाडी (छिद्र खोलीद्वारे) 50Mil असल्यास, PCB उत्पादक सामान्य परिस्थितीत प्रदान करू शकणारा किमान ड्रिलिंग व्यास केवळ 8Mil पर्यंत पोहोचू शकतो. लेसर ड्रिलिंग तंत्रज्ञानाच्या विकासासह, ड्रिलिंगचा आकार देखील लहान आणि लहान असू शकतो आणि छिद्राचा व्यास साधारणपणे 6Mils पेक्षा कमी किंवा समान असतो, आम्हाला मायक्रोहोल म्हणतात.

मायक्रोहोलचा वापर एचडीआय (उच्च घनता इंटरकनेक्ट स्ट्रक्चर) डिझाइनमध्ये केला जातो आणि मायक्रोहोल तंत्रज्ञानामुळे थेट पॅडवर छिद्र पाडले जाऊ शकते, ज्यामुळे सर्किटची कार्यक्षमता मोठ्या प्रमाणात सुधारते आणि वायरिंगची जागा वाचते. वाया ट्रान्समिशन लाईनवरील प्रतिबाधा विघटनाचा ब्रेकपॉईंट म्हणून दिसून येतो, ज्यामुळे सिग्नलचे प्रतिबिंब होते. सामान्यतः, होलचा समतुल्य प्रतिबाधा ट्रान्समिशन लाइनपेक्षा सुमारे 12% कमी असतो, उदाहरणार्थ, 50 ohms ट्रान्समिशन लाइनचा प्रतिबाधा जेव्हा छिद्रातून जातो तेव्हा 6 ohms ने कमी केला जातो (विशेषतः आणि मार्गाचा आकार, प्लेटची जाडी देखील संबंधित आहे, पूर्ण घट नाही).

तथापि, द्वारे प्रतिबाधा खंडित झाल्यामुळे होणारे प्रतिबिंब प्रत्यक्षात खूपच लहान आहे आणि त्याचे प्रतिबिंब गुणांक फक्त आहे:

(४४-५०)/(४४ + ५०) = ०.०६

मार्गातून उद्भवलेल्या समस्या परजीवी कॅपेसिटन्स आणि इंडक्टन्सच्या प्रभावांवर अधिक केंद्रित आहेत.

Via चे परजीवी कॅपेसिटन्स आणि इंडक्टन्स

स्वतः मध्ये एक परजीवी स्ट्रे कॅपेसिटन्स आहे. जर घातलेल्या थरावरील सोल्डर रेझिस्टन्स झोनचा व्यास D2 असेल, सोल्डर पॅडचा व्यास D1 असेल, PCB बोर्डची जाडी T असेल आणि सब्सट्रेटचा डायलेक्ट्रिक स्थिरांक ε असेल, तर थ्रू होलची परजीवी कॅपेसिटन्स अंदाजे आहे:

C=1.41εTD1/(D2-D1)

सर्किटवरील परजीवी कॅपेसिटन्सचा मुख्य परिणाम म्हणजे सिग्नलचा उदय वेळ लांबवणे आणि सर्किटची गती कमी करणे.

उदाहरणार्थ, 50Mil ची जाडी असलेल्या PCB साठी, जर वाया पॅडचा व्यास 20Mil (ड्रिलिंग होलचा व्यास 10Mil आहे) आणि सोल्डर रेझिस्टन्स झोनचा व्यास 40Mil असेल, तर आपण अंदाजे परजीवी कॅपेसिटन्स मोजू शकतो. वरील सूत्रानुसार:

C=1.41x4.4x0.050x0.020/(0.040-0.020)=0.31pF

कॅपॅसिटन्सच्या या भागामुळे होणारी वाढ वेळ बदल अंदाजे आहे:

T10-90=2.2C(Z0/2)=2.2x0.31x(50/2)=17.05ps

या मूल्यांवरून हे लक्षात येते की सिंगल via च्या परजीवी कॅपॅसिटन्समुळे होणाऱ्या वाढीच्या विलंबाची उपयुक्तता फारशी स्पष्ट नसली तरी, स्तरांमध्ये स्विच करण्यासाठी via अनेक वेळा ओळीत वापरल्यास, अनेक छिद्रे वापरली जातील, आणि डिझाइन काळजीपूर्वक विचारात घेतले पाहिजे. वास्तविक डिझाइनमध्ये, छिद्र आणि तांबे क्षेत्र (अँटी-पॅड) मधील अंतर वाढवून किंवा पॅडचा व्यास कमी करून परजीवी कॅपेसिटन्स कमी करता येतो.

हाय-स्पीड डिजिटल सर्किट्सच्या डिझाइनमध्ये, परजीवी इंडक्टन्समुळे होणारी हानी परजीवी कॅपेसिटन्सच्या प्रभावापेक्षा जास्त असते. त्याची परजीवी मालिका इंडक्टन्स बायपास कॅपेसिटरचे योगदान कमकुवत करेल आणि संपूर्ण उर्जा प्रणालीची फिल्टरिंग प्रभावीता कमकुवत करेल.

थ्रू-होल अंदाजे परजीवी इंडक्टन्सची गणना करण्यासाठी आम्ही खालील अनुभवजन्य सूत्र वापरू शकतो:

L=5.08h[ln(4h/d)+1]

जेथे L हा via च्या इंडक्टन्सचा संदर्भ देतो, h ही via ची लांबी आहे आणि d हा मध्यवर्ती छिद्राचा व्यास आहे. सूत्रावरून असे दिसून येते की वायाच्या व्यासाचा इंडक्टन्सवर फारसा प्रभाव पडत नाही, तर व्हियाच्या लांबीचा इंडक्टन्सवर सर्वात जास्त प्रभाव असतो. तरीही वरील उदाहरण वापरून, आउट-ऑफ-होल इंडक्टन्सची गणना खालीलप्रमाणे केली जाऊ शकते:

L=5.08x0.050[ln(4x0.050/0.010)+1]=1.015nH

जर सिग्नलचा उदय वेळ 1ns असेल, तर त्याचा समतुल्य प्रतिबाधा आकार आहे:

XL=πL/T10-90=3.19Ω

उच्च-वारंवारता प्रवाहाच्या उपस्थितीत अशा प्रतिबाधाकडे दुर्लक्ष केले जाऊ शकत नाही, विशेषतः लक्षात घ्या की बायपास कॅपेसिटरला पॉवर लेयर आणि फॉर्मेशन जोडताना दोन छिद्रांमधून जाणे आवश्यक आहे, जेणेकरून भोकातील परजीवी इंडक्टन्स गुणाकार केला जाईल.

द्वारे कसे वापरावे?

भोकांच्या परजीवी वैशिष्ट्यांच्या वरील विश्लेषणाद्वारे, आम्ही पाहू शकतो की हाय-स्पीड पीसीबी डिझाइनमध्ये, वरवर साधे दिसणारे छिद्र सर्किटच्या डिझाइनवर बरेच नकारात्मक प्रभाव आणतात. छिद्राच्या परजीवी प्रभावामुळे होणारे प्रतिकूल परिणाम कमी करण्यासाठी, डिझाइन शक्य तितके असू शकते:

किंमत आणि सिग्नल गुणवत्ता या दोन पैलूंमधून, वाजवी आकाराचा आकार निवडा. आवश्यक असल्यास, तुम्ही वीज पुरवठा किंवा ग्राउंड वायर होल यांसारख्या विविध आकाराच्या वायस वापरण्याचा विचार करू शकता, तुम्ही प्रतिबाधा कमी करण्यासाठी मोठा आकार वापरण्याचा विचार करू शकता आणि सिग्नल वायरिंगसाठी, तुम्ही लहान व्हाया वापरू शकता. अर्थात, व्हायाचा आकार जसजसा कमी होईल तसतसा संबंधित खर्चही वाढेल

वर चर्चा केलेल्या दोन सूत्रांवरून असा निष्कर्ष काढला जाऊ शकतो की पातळ पीसीबी बोर्डचा वापर दोन परजीवी पॅरामीटर्स कमी करण्यासाठी अनुकूल आहे.

पीसीबी बोर्डवरील सिग्नल वायरिंग शक्यतोवर बदलू नये, म्हणजेच अनावश्यक विस न वापरण्याचा प्रयत्न करा.

वीज पुरवठ्याच्या पिन आणि जमिनीवर वायस ड्रिल करणे आवश्यक आहे. पिन आणि व्हियासमधील शिसे जितके लहान असतील तितके चांगले. समतुल्य इंडक्टन्स कमी करण्यासाठी समांतर मध्ये अनेक छिद्रे ड्रिल केली जाऊ शकतात.

सिग्नलसाठी सर्वात जवळचा लूप देण्यासाठी सिग्नल बदलाच्या थ्रू-होलजवळ काही ग्राउंड केलेले थ्रू-होल ठेवा. तुम्ही PCB बोर्डवर काही अतिरिक्त ग्राउंड होल देखील ठेवू शकता.

उच्च घनतेसह हाय स्पीड पीसीबी बोर्डसाठी, आपण मायक्रो-होल वापरण्याचा विचार करू शकता.