पीसीबी डिझाइनच्या प्रक्रियेत, पॉवर प्लेनचे विभाजन किंवा ग्राउंड प्लेनचे विभाजन अपूर्ण विमानास कारणीभूत ठरेल. अशाप्रकारे, जेव्हा सिग्नल रूट केला जातो, तेव्हा त्याचे संदर्भ विमान एका पॉवर प्लेनपासून दुसर्या पॉवर प्लेनपर्यंत पसरते. या इंद्रियगोचरला सिग्नल स्पॅन विभाग म्हणतात.

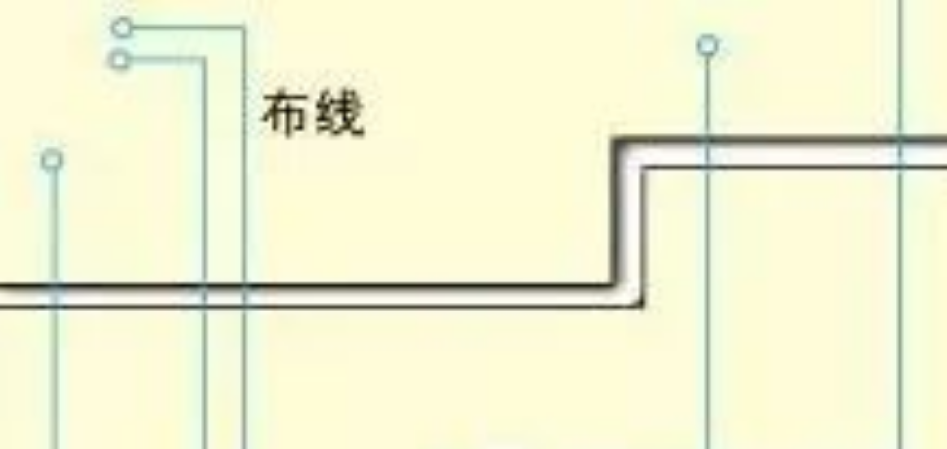

क्रॉस-सेगमेंटेशन इंद्रियगोचरचे योजनाबद्ध आकृती

क्रॉस सेगमेंटेशन, कमी स्पीड सिग्नलसाठी कोणताही संबंध असू शकत नाही, परंतु हाय स्पीड डिजिटल सिग्नल सिस्टममध्ये, हाय स्पीड सिग्नल संदर्भ विमानास परतीचा मार्ग, म्हणजेच रिटर्न पथ म्हणून घेते. जेव्हा संदर्भ विमान अपूर्ण असेल, तेव्हा खालील प्रतिकूल परिणाम उद्भवतील: क्रॉस-सेगमेंटेशन कमी-स्पीड सिग्नलसाठी संबंधित असू शकत नाही, परंतु हाय-स्पीड डिजिटल सिग्नल सिस्टममध्ये, हाय-स्पीड सिग्नल संदर्भ विमानास परतीचा मार्ग म्हणून घेतात, म्हणजेच रिटर्न पथ. जेव्हा संदर्भ विमान अपूर्ण असेल, तेव्हा खालील प्रतिकूल परिणाम उद्भवतील:

एल प्रतिबाधा विसंगतीमुळे वायर चालू होते;

l सिग्नल दरम्यान क्रॉस्टलॉक कारणीभूत;

l हे सिग्नल दरम्यान प्रतिबिंबित करते;

l वर्तमान आणि लूपच्या इंडक्टन्सचे लूप क्षेत्र वाढवून आउटपुट वेव्हफॉर्म ओसीलेट करणे सोपे आहे.

l जागेत रेडिएशन हस्तक्षेप वाढविला जातो आणि अंतराळातील चुंबकीय क्षेत्राचा सहज परिणाम होतो.

l बोर्डवरील इतर सर्किट्ससह चुंबकीय जोडण्याची शक्यता वाढवते;

l लूप इंडक्टरवरील उच्च वारंवारता व्होल्टेज ड्रॉप सामान्य-मोड रेडिएशन स्त्रोत तयार करते, जे बाह्य केबलद्वारे व्युत्पन्न होते.

म्हणून, पीसीबी वायरिंग शक्य तितक्या विमानाच्या जवळ असावे आणि क्रॉस-डिव्हिजन टाळावे. जर विभाग ओलांडणे आवश्यक असेल किंवा पॉवर ग्राउंड प्लेनच्या जवळ नसेल तर या अटी केवळ कमी वेगाच्या सिग्नल लाइनमध्ये परवानगी आहेत.

डिझाइनमध्ये विभाजन ओलांडून प्रक्रिया

जर पीसीबी डिझाइनमध्ये क्रॉस-डिव्हिजन अपरिहार्य असेल तर त्यास कसे सामोरे जावे? या प्रकरणात, सिग्नलसाठी एक लहान रिटर्न पथ प्रदान करण्यासाठी विभाजन सुधारणे आवश्यक आहे. सामान्य प्रक्रियेच्या पद्धतींमध्ये मेंडिंग कॅपेसिटर जोडणे आणि वायर ब्रिज ओलांडणे समाविष्ट आहे.

एल स्टिचिंग कॅपेसिटर

0402 किंवा 0603 सिरेमिक कॅपेसिटर 0.01UF किंवा 0.1UF च्या क्षमतेसह सामान्यत: सिग्नल क्रॉस विभागात ठेवला जातो. जर स्पेस परवानगी दिली तर अशा अनेक कॅपेसिटर जोडले जाऊ शकतात.

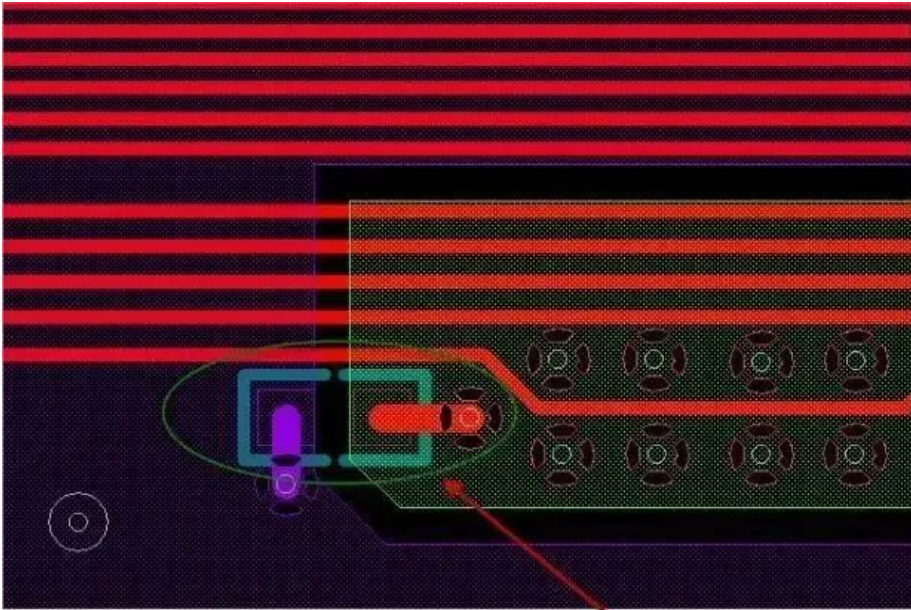

त्याच वेळी, सिग्नल वायर 200 मिल मिल शिवणकामाच्या कॅपेसिटन्सच्या श्रेणीत आहे हे सुनिश्चित करण्याचा प्रयत्न करा आणि जितके लहान अंतर तितके चांगले आहे; कॅपेसिटरच्या दोन्ही टोकावरील नेटवर्क अनुक्रमे संदर्भ विमानाच्या नेटवर्कशी संबंधित आहेत ज्याद्वारे सिग्नल पास करतात. खालील आकृतीमध्ये कॅपेसिटरच्या दोन्ही टोकांवर कनेक्ट केलेले नेटवर्क पहा. दोन रंगांमध्ये हायलाइट केलेले दोन भिन्न नेटवर्क आहेतः

एलवायर ओव्हर पूल

सिग्नल लेयरमधील विभागातील सिग्नल "ग्राउंड प्रक्रिया" करणे सामान्य आहे आणि इतर नेटवर्क सिग्नल लाइन देखील असू शकतात, शक्य तितक्या जाड “ग्राउंड” लाइन

हाय स्पीड सिग्नल वायरिंग कौशल्ये

अ)मल्टीलेयर इंटरकनेक्शन

हाय स्पीड सिग्नल रूटिंग सर्किटमध्ये बर्याचदा उच्च एकत्रीकरण असते, वायरिंगची उच्च घनता असते, मल्टीलेयर बोर्ड वापरणे केवळ वायरिंगसाठीच आवश्यक नसते, तर हस्तक्षेप कमी करण्यासाठी एक प्रभावी साधन देखील असते.

थरांची वाजवी निवड प्रिंटिंग बोर्डचा आकार मोठ्या प्रमाणात कमी करू शकते, शील्ड सेट करण्यासाठी इंटरमीडिएट लेयरचा पूर्ण वापर करू शकतो, जवळपासच्या ग्राउंडिंगला अधिक चांगल्या प्रकारे लक्षात येऊ शकते, परजीवी इंडक्शनन्स प्रभावीपणे कमी करू शकते, सिग्नलची प्रसारणाची लांबी प्रभावीपणे कमी करू शकते, सिग्नल इत्यादींमधील क्रॉस हस्तक्षेप मोठ्या प्रमाणात कमी करू शकते.

बी)आघाडी जितकी कमी वाकली तितकी चांगली

हाय-स्पीड सर्किट डिव्हाइसच्या पिन दरम्यान कमी लीड वाकणे, चांगले.

हाय-स्पीड सिग्नल रूटिंग सर्किटची वायरिंग लीड पूर्ण सरळ रेषा स्वीकारते आणि ती चालू करणे आवश्यक आहे, जे 45 ° पॉलीलाइन किंवा आर्क टर्निंग म्हणून वापरले जाऊ शकते. ही आवश्यकता केवळ कमी-वारंवारता सर्किटमध्ये स्टील फॉइलची धारण करणारी शक्ती सुधारण्यासाठी वापरली जाते.

हाय-स्पीड सर्किट्समध्ये, ही आवश्यकता पूर्ण केल्याने हाय-स्पीड सिग्नलचे प्रसारण आणि जोडणी कमी होऊ शकते आणि सिग्नलचे रेडिएशन आणि प्रतिबिंब कमी होऊ शकते.

सी)आघाडी जितकी लहान असेल तितके चांगले

हाय-स्पीड सिग्नल रूटिंग सर्किट डिव्हाइसच्या पिन दरम्यानची आघाडी जितकी लहान असेल तितके चांगले.

आघाडी जितकी जास्त असेल तितकी वितरित इंडक्टन्स आणि कॅपेसिटन्स मूल्य, ज्याचा सिस्टमच्या उच्च-वारंवारतेच्या सिग्नल पासिंगवर खूप प्रभाव होईल, परंतु सर्किटचे वैशिष्ट्यपूर्ण प्रतिबाधा देखील बदलते, परिणामी सिस्टमचे प्रतिबिंब आणि दोलन होते.

डी)लीड लेयर्स दरम्यान कमी बदल, चांगले

हाय-स्पीड सर्किट डिव्हाइसच्या पिन दरम्यान कमी इंटरलेयर अल्टरनेशन्स, चांगले.

तथाकथित “लीड्सचे कमी इंटरलेयर अल्टरनेशन्स, चांगले” म्हणजे घटकांच्या कनेक्शनमध्ये वापरल्या जाणार्या कमी छिद्र, अधिक चांगले. हे मोजले गेले आहे की एक छिद्र वितरित कॅपेसिटन्सचे 0.5 पीएफ आणू शकते, परिणामी सर्किट विलंबात लक्षणीय वाढ होऊ शकते, ज्यामुळे छिद्रांची संख्या कमी होऊ शकते.

ई)समांतर क्रॉस हस्तक्षेप लक्षात घ्या

हाय-स्पीड सिग्नल वायरिंगने सिग्नल लाइन शॉर्ट अंतर समांतर वायरिंगद्वारे सादर केलेल्या “क्रॉस हस्तक्षेप” कडे लक्ष दिले पाहिजे. जर समांतर वितरण टाळता येत नसेल तर, हस्तक्षेप कमी करण्यासाठी समांतर सिग्नल लाइनच्या उलट बाजूस “ग्राउंड” चे मोठे क्षेत्र व्यवस्थित केले जाऊ शकते.

एफ)शाखा आणि स्टंप टाळा

हाय-स्पीड सिग्नल वायरिंगने शाखा किंवा स्टब तयार करणे टाळले पाहिजे.

स्टंपचा प्रतिबाधावर चांगला परिणाम होतो आणि सिग्नल प्रतिबिंब आणि ओव्हरशूट होऊ शकतो, म्हणून आम्ही सहसा डिझाइनमध्ये स्टंप आणि शाखा टाळली पाहिजेत.

डेझी चेन वायरिंग सिग्नलवरील परिणाम कमी करेल.

g)सिग्नल ओळी शक्य तितक्या आतल्या मजल्यावर जातात

पृष्ठभागावर उच्च वारंवारता सिग्नल लाइन चालणे मोठे इलेक्ट्रोमॅग्नेटिक रेडिएशन तयार करणे सोपे आहे आणि बाह्य इलेक्ट्रोमॅग्नेटिक रेडिएशन किंवा घटकांद्वारे हस्तक्षेप करणे देखील सोपे आहे.

वीजपुरवठा आणि ग्राउंड वायर दरम्यान उच्च वारंवारता सिग्नल लाइन वीज पुरवठा आणि तळाशी थर द्वारे इलेक्ट्रोमॅग्नेटिक वेव्हच्या शोषणाद्वारे, तयार केलेले रेडिएशन बरेच कमी केले जाईल.