जर इंटरलेयर कॅपेसिटन्स पुरेसे मोठे नसेल तर विद्युत क्षेत्र बोर्डच्या तुलनेने मोठ्या क्षेत्रावर वितरित केले जाईल, जेणेकरून इंटरलेयर प्रतिबाधा कमी होईल आणि रिटर्न करंट वरच्या थरात परत येऊ शकेल. या प्रकरणात, या सिग्नलद्वारे व्युत्पन्न केलेले फील्ड जवळच्या बदलत्या लेयर सिग्नलच्या फील्डमध्ये हस्तक्षेप करू शकते. आम्ही ज्याची अपेक्षा केली होती तेच नाही. दुर्दैवाने, 0.062 इंचाच्या 4-लेयर बोर्डवर, थर बरेच दूर आहेत आणि इंटरलेयर कॅपेसिटन्स लहान आहे

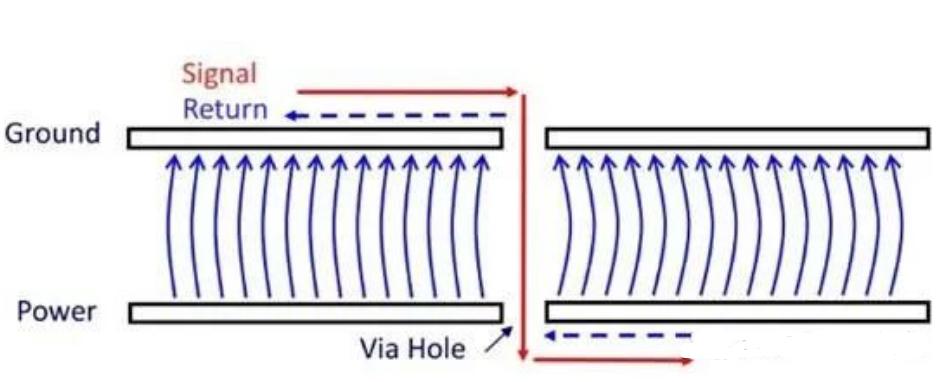

जेव्हा वायरिंग लेयर 1 वरून लेयर 4 किंवा त्याउलट बदलते तेव्हा या समस्येचे चित्र म्हणून दर्शविले जाईल

आकृती दर्शविते की जेव्हा सिग्नल लेयर 1 ते लेयर 4 (रेड लाइन) पर्यंत ट्रॅक करतो तेव्हा रिटर्न करंटमध्ये विमान (ब्लू लाइन) देखील बदलणे आवश्यक आहे. जर सिग्नलची वारंवारता जास्त प्रमाणात असेल आणि विमाने एकत्र असतील तर, रिटर्न करंट ग्राउंड लेयर आणि पॉवर लेयर दरम्यान अस्तित्त्वात असलेल्या इंटरलेयर कॅपेसिटन्समधून वाहू शकतो. तथापि, रिटर्न करंटसाठी थेट प्रवाहकीय कनेक्शन नसल्यामुळे, परतीचा मार्ग व्यत्यय आणला आहे आणि आम्ही या व्यत्ययाचा विचार करू शकतो की खालील चित्रात दर्शविलेल्या विमानांमधील अडथळा म्हणून आम्ही विचार करू शकतो

जर इंटरलेयर कॅपेसिटन्स पुरेसे मोठे नसेल तर विद्युत क्षेत्र बोर्डच्या तुलनेने मोठ्या क्षेत्रावर वितरित केले जाईल, जेणेकरून इंटरलेयर प्रतिबाधा कमी होईल आणि रिटर्न करंट वरच्या थरात परत येऊ शकेल. या प्रकरणात, या सिग्नलद्वारे व्युत्पन्न केलेले फील्ड जवळच्या बदलत्या लेयर सिग्नलच्या फील्डमध्ये हस्तक्षेप करू शकते. आम्ही ज्याची अपेक्षा केली होती तेच नाही. दुर्दैवाने, 0.062 इंचाच्या 4-लेयर बोर्डवर, थर बरेच दूर आहेत (कमीतकमी 0.020 इंच) आणि इंटरलेयर कॅपेसिटन्स लहान आहे. परिणामी, वर वर्णन केलेले इलेक्ट्रिक फील्ड हस्तक्षेप उद्भवते. यामुळे सिग्नल अखंडतेच्या समस्येस कारणीभूत ठरू शकत नाही, परंतु यामुळे अधिक ईएमआय तयार होईल. म्हणूनच, कॅसकेड वापरताना आम्ही थर बदलणे टाळतो, विशेषत: घड्याळांसारख्या उच्च वारंवारता सिग्नलसाठी.

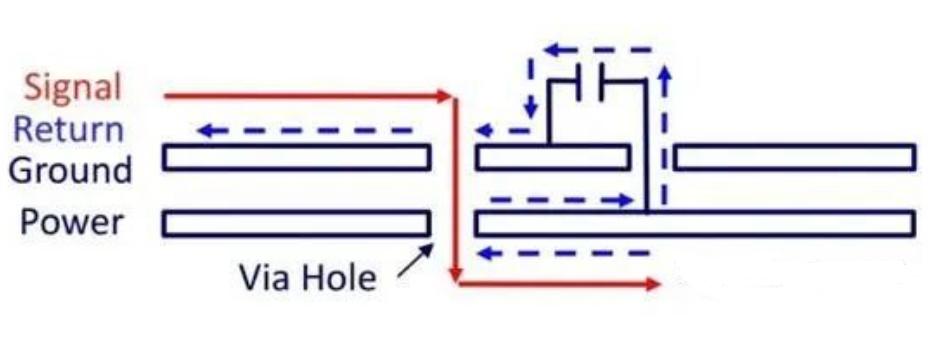

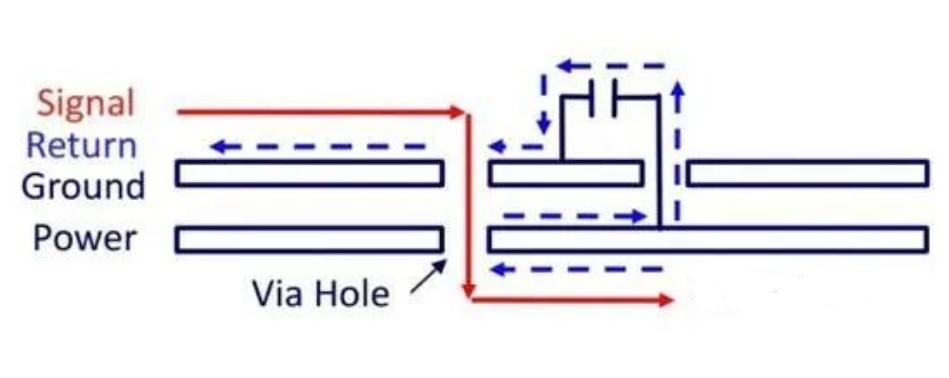

खालील चित्रानुसार दर्शविलेल्या परतीच्या वर्तमानातून अनुभवलेली प्रतिबाधा कमी करण्यासाठी संक्रमण पास होलजवळ डिकॉपलिंग कॅपेसिटर जोडणे ही सामान्य पद्धत आहे. तथापि, कमी स्व-रेझोनंट वारंवारतेमुळे व्हीएचएफ सिग्नलसाठी हे डिकॉपलिंग कॅपेसिटर कुचकामी आहे. 200-300 मेगाहर्ट्झपेक्षा जास्त फ्रिक्वेन्सी असलेल्या एसी सिग्नलसाठी, आम्ही कमी-इम्पेडन्स रिटर्न मार्ग तयार करण्यासाठी डिकॉपलिंग कॅपेसिटरवर अवलंबून राहू शकत नाही. म्हणूनच, आम्हाला डिकॉपलिंग कॅपेसिटर (200-300 मेगाहर्ट्झच्या खाली) आणि उच्च वारंवारतेसाठी तुलनेने मोठा इंटरबोर्ड कॅपेसिटर आवश्यक आहे.

की सिग्नलचा थर न बदलून ही समस्या टाळली जाऊ शकते. तथापि, फोर-लेयर बोर्डाच्या छोट्या इंटरबोर्ड कॅपेसिटन्समुळे आणखी एक गंभीर समस्या उद्भवते: उर्जा प्रसारण. घड्याळ डिजिटल आयसींना सामान्यत: मोठ्या क्षणिक वीजपुरवठा प्रवाहांची आवश्यकता असते. आयसी आउटपुटची वाढ/गडी बाद होण्याचा क्रम कमी होत असताना, आम्हाला उच्च दराने ऊर्जा वितरित करण्याची आवश्यकता आहे. चार्ज स्रोत प्रदान करण्यासाठी, आम्ही सहसा प्रत्येक लॉजिक आयसीच्या अगदी जवळ डिकॉपलिंग कॅपेसिटर ठेवतो. तथापि, एक समस्या आहे: जेव्हा आपण स्वयं-पुनर्विचार वारंवारतेच्या पलीकडे जातो, तेव्हा डिकॉपलिंग कॅपेसिटर कार्यक्षमतेने ऊर्जा संचयित आणि हस्तांतरित करू शकत नाहीत, कारण या फ्रिक्वेन्सीवर कॅपेसिटर इंडक्टरसारखे कार्य करेल.

आज बहुतेक आयसीएसमध्ये वेगवान वाढ/गडी बाद होण्याचा क्रम (सुमारे 500 पीएस) असल्याने, आम्हाला डिकॉपलिंग कॅपेसिटरपेक्षा उच्च स्व-रेझोनंट वारंवारतेसह अतिरिक्त डिकॉपलिंग स्ट्रक्चरची आवश्यकता आहे. सर्किट बोर्डचे इंटरलेयर कॅपेसिटन्स एक प्रभावी डिकॉपलिंग स्ट्रक्चर असू शकते, परंतु जर पुरेसे कॅपेसिटन्स प्रदान करण्यासाठी थर एकमेकांना पुरेसे जवळ असतील. म्हणूनच, सामान्यत: वापरल्या जाणार्या डिकॉपलिंग कॅपेसिटर व्यतिरिक्त, आम्ही डिजिटल आयसींना क्षणिक शक्ती प्रदान करण्यासाठी जवळून अंतरावरील उर्जा स्तर आणि ग्राउंड लेयर्स वापरणे पसंत करतो.

कृपया लक्षात घ्या की कॉमन सर्किट बोर्ड उत्पादन प्रक्रियेमुळे आमच्याकडे सहसा चार-लेयर बोर्डच्या दुसर्या आणि तिसर्या थरांमध्ये पातळ इन्सुलेटर नसतात. दुसर्या आणि तिसर्या थरांमधील पातळ इन्सुलेटरसह चार-स्तरावरील बोर्ड पारंपारिक चार-स्तर बोर्डापेक्षा जास्त खर्च करू शकतो.