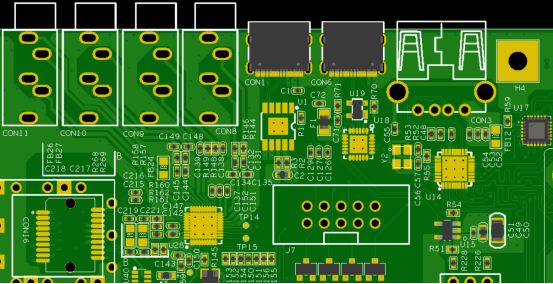

Kalbant apie PCB išdėstymo ir laidų problemą, šiandien nekalbėsime apie signalo vientisumo analizę (SI), elektromagnetinio suderinamumo analizę (EMC), galios vientisumo analizę (PI). Tiesiog kalbant apie gaminamumo analizę (DFM), nepagrįstas gaminamumo dizainas taip pat lems produkto dizainą.

Sėkmingas DFM PCB išdėstymas prasideda nuo projektavimo taisyklių nustatymo, atsižvelgiant į svarbius DFM apribojimus. Žemiau pateiktos DFM taisyklės atspindi kai kurias šiuolaikinių projektavimo galimybes, kurias gali rasti dauguma gamintojų. Įsitikinkite, kad PCB projektavimo taisyklėse nustatytos ribos jų nepažeidžia, kad būtų užtikrinta dauguma standartinių dizaino apribojimų.

PCB maršruto DFM problema priklauso nuo gero PCB išdėstymo, o maršruto parinkimo taisyklės gali būti nustatytos, įskaitant linijos lenkimo laiko skaičių, laidumo skylių skaičių, žingsnių skaičių ir tt. Visuotinis maršruto parinkimo kelio optimizavimas pirmiausia atliekamas laiduose, o pertvarkymas bandomas pagerinti bendrą efektą ir DFM gamintoją.

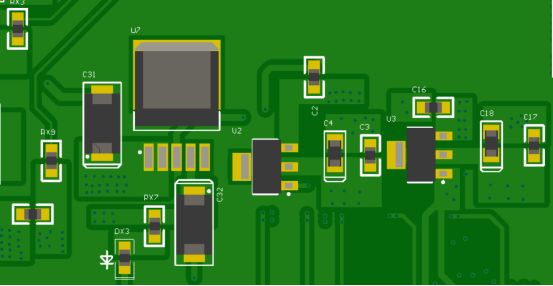

1.SMT įrenginiai

Įrenginio išdėstymo tarpai atitinka surinkimo reikalavimus ir paprastai yra didesnis nei 20 mln. Paviršiaus pritvirtintų įtaisų, 80 mln. Siekiant pagerinti gamybos proceso kokybę ir išeigą, tarpai tarp prietaisų gali atitikti surinkimo reikalavimus.

Paprastai atstumas tarp prietaiso kaiščių SMD trinkelių turėtų būti didesnis nei 6 mln., O litavimo litavimo tilto gamybos talpa yra 4 mln. Jei atstumas tarp SMD trinkelių yra mažesnis nei 6 mln., O atstumas tarp litavimo lango yra mažesnis nei 4 mil, litavimo tilto negalima išlaikyti, todėl surinkimo proceso metu yra dideli litavimo elementai (ypač tarp kaiščių), o tai sukels trumpą jungimą.

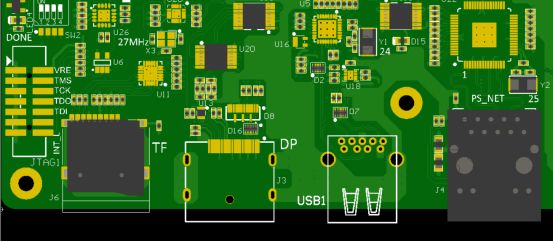

2.Dip įrenginys

Reikia atsižvelgti į kaiščio tarpus, kryptis ir tarpai ir tarpai, esantys per bangų litavimo procesą. Nepakankamas prietaiso tarpo kaiščiuose atsiras litavimo skardos litavimo, o tai sukels trumpą jungimą.

Daugelis dizainerių sumažina internetinių įrenginių (THT) naudojimą arba padeda juos toje pačioje lentos pusėje. Tačiau internetiniai prietaisai dažnai neišvengiami. Derinio atveju, jei vidinis įtaisas dedamas ant viršutinio sluoksnio, o pleistro įtaisas dedamas ant apatinio sluoksnio, kai kuriais atvejais jis paveiks vienos pusės bangų litavimą. Šiuo atveju naudojami brangesni suvirinimo procesai, tokie kaip selektyvus suvirinimas.

3. Atstumas tarp komponentų ir plokštelės krašto

Jei tai yra mašinų suvirinimas, atstumas tarp elektroninių komponentų ir plokštės krašto paprastai yra 7 mm (skirtingi suvirinimo gamintojai turi skirtingus reikalavimus), tačiau jį taip pat galima pridėti PCB gamybos proceso krašte, kad elektroninius komponentus būtų galima dėti ant PCB plokštės krašto, jei tai yra patogu laidų laidai.

Tačiau kai plokštės kraštas suvirinamas, jis gali susidurti su mašinos kreipiamu bėgiu ir sugadinti komponentus. Prietaiso padėklas plokštelės krašte bus pašalintas gamybos procese. Jei padėkliuką maža, suvirinimo kokybė turės įtakos.

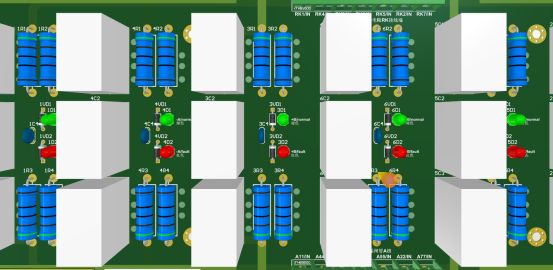

4. Aukštų/žemų prietaisų keitimas

Yra daugybė elektroninių komponentų rūšių, skirtingų formų ir įvairių švino linijų, todėl spausdintų plokščių surinkimo metodas skiriasi. Geras išdėstymas gali ne tik padaryti mašiną stabilų našumą, įrodyti smūgį, sumažinti žalą, bet ir gauti tvarkingą ir gražų efektą mašinoje.

Maži prietaisai turi būti laikomi tam tikru atstumu aplink aukštus prietaisus. Įrenginio atstumas iki prietaiso aukščio santykio yra mažas, yra nelygus šiluminė banga, dėl kurios po suvirinimo gali kilti blogo suvirinimo ar taisymo rizika.

5.Devifika į įrenginio tarpus

Apskritai SMT apdorojimui būtina atsižvelgti į tam tikras mašinos montavimo klaidas ir atsižvelgti į techninės priežiūros ir vaizdinio patikrinimo patogumą. Du gretimi komponentai neturėtų būti per arti, o tam tikras saugus atstumas turėtų būti paliktas.

Tarpai tarp dribsnių komponentų, SOT, SOIC ir dribsnių komponentų yra 1,25 mm. Tarpai tarp dribsnių komponentų, SOT, SOIC ir dribsnių komponentų yra 1,25 mm. 2,5 mm tarp PLCC ir dribsnių komponentų, SOIC ir QFP. 4 mm tarp PLCC. Projektuojant PLCC lizdus, reikia pasirūpinti, kad būtų galima nustatyti PLCC lizdo dydį (PLCC kaištis yra lizdo apačioje).

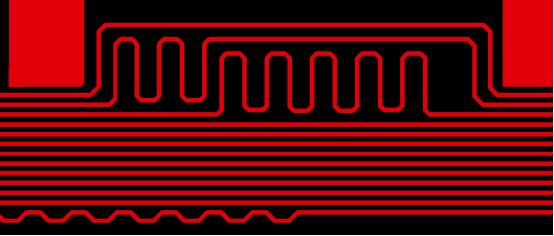

6. Linijos plotis/linijos atstumas

Dizaineriams projektavimo procese galime ne tik atsižvelgti į projektavimo reikalavimų tikslumą ir tobulumą, bet ir didelis apribojimas yra gamybos procesas. Lentos gamykloje neįmanoma sukurti naujos gamybos linijos, skirtos gimti geras produktas.

Normaliomis sąlygomis žemyn linijos linijos plotis kontroliuojamas iki 4/4 mil, o skylė pasirinkta kaip 8 mil (0,2 mm). Iš esmės daugiau nei 80% PCB gamintojų gali gaminti, o gamybos kaina yra mažiausia. Mažiausią linijos plotį ir linijos atstumą galima valdyti iki 3/3 mil, o per skylę galima pasirinkti 6 mln. (0,15 mm). Iš esmės daugiau nei 70% PCB gamintojų gali jį gaminti, tačiau kaina yra šiek tiek didesnė nei pirmasis atvejis, ne per daug didesnis.

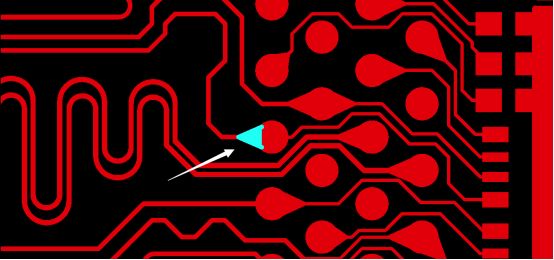

7. ūmus kampas/stačiu kampas

Sąmoningumo kampo maršrutizavimas paprastai draudžiamas laidų metu, paprastai reikalingas stačiakampio maršrutas, kad būtų išvengta situacijos PCB maršrute, ir beveik tapo vienu iš standartų, leidžiančių išmatuoti laidų kokybę. Kadangi paveiktas signalo vientisumas, dešiniojo kampo laidai sukels papildomą parazitinę talpą ir induktyvumą.

PCB plokštelių kūrimo procese PCB laidai susikerta ūmiu kampu, o tai sukels problemą, vadinamą rūgšties kampu. PCB grandinės ėsdinimo jungtyje per didelis PCB grandinės korozija bus sukelta esant „rūgšties kampui“, todėl PCB grandinės virtualios lūžio problema. Todėl PCB inžinieriams reikia vengti aštrių ar keistų laidų kampų ir palaikyti 45 laipsnių kampą laidų kampe.

8.Kopperė juosta/sala

Jei tai yra pakankamai didelis salos vario, jis taps antena, kuri gali sukelti triukšmą ir kitus trukdžius lentos viduje (nes jo varis nėra įžemintas, jis taps signalo kolekcionieriumi).

Vario juostelės ir salos yra daugybė plokščio vario, kuris gali sukelti rimtų problemų rūgščioje lovelėje, sluoksniai. Buvo žinoma, kad mažos vario dėmės nutraukia PCB skydą ir keliauja į kitas išgraviruotas skydelio vietas, sukeldamas trumpą jungimą.

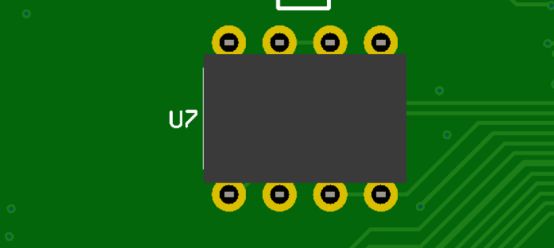

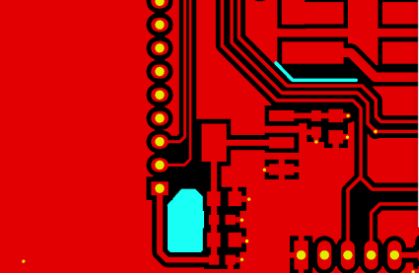

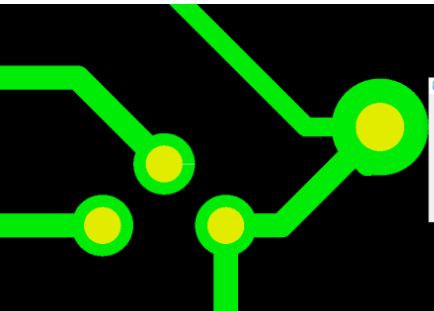

9.Kolio gręžimo skylių žiedas

Skylių žiedas nurodo vario žiedą aplink gręžimo angą. Dėl gamybos proceso nuokrypių, po gręžimo, ėsdinimo ir vario dengimo, likęs vario žiedas aplink gręžimo angą ne visada puikiai atsitrenkia į padėkliuko vidurio tašką, dėl kurio skylės žiedas gali nutrūkti.

Viena skylės žiedo pusė turi būti didesnė nei 3,5 mln., O papildinio skylių žiedas turi būti didesnis nei 6 mln. Skylių žiedas yra per mažas. Gamybos ir gamybos metu gręžimo skylė turi toleranciją, o linijos suderinimas taip pat turi toleranciją. Dėl nuokrypio nuokrypio, skylių žiedas sulaužys atvirą grandinę.

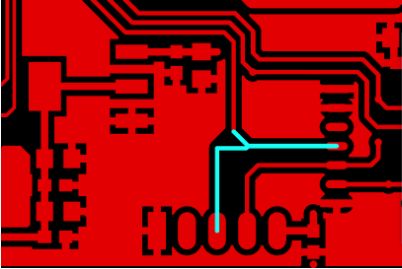

10. Laidų ašarų lašai

Pridėjus ašarų prie PCB laidų, PCB plokštės grandinės jungtis gali padaryti stabilesnį, didelį patikimumą, kad sistema būtų stabilesnė, todėl reikia pridėti ašarų prie plokštės.

Pridėjus ašarų lašų, gali būti išvengta kontaktinio taško tarp vielos ir padėklo ar vielos atjungimo bei bandomosios skylės, kai grandinės lentą paveikia didžiulė išorinė jėga. Pridedant ašarų lašus prie suvirinimo, jis gali apsaugoti trinkelę, išvengti kelių suvirinimo, kad padėkliuką nukritų, ir išvengti nelygaus ėsdinimo ir įtrūkimų, kuriuos sukelia skylės deformacija gamybos metu.