VIA yra vienas iš svarbių daugiasluoksnio PCB komponentų, o gręžimo išlaidos paprastai sudaro nuo 30 iki 40% PCB plokštės kainos. Paprasčiau tariant, kiekviena PCB skylė gali būti vadinama A Via.

Pagrindinė VIA:

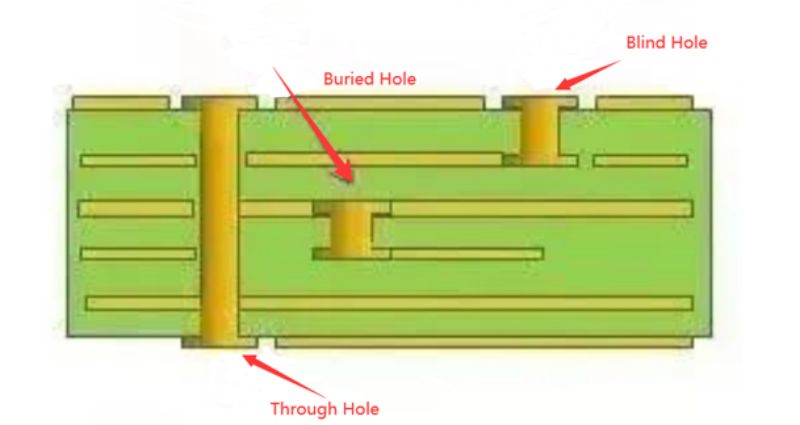

Funkcijos požiūriu VIA galima suskirstyti į dvi kategorijas: viena naudojama kaip elektrinė jungtis tarp sluoksnių, o kita naudojama kaip prietaiso tvirtinimas ar padėtis. Jei iš proceso, šios skylės paprastai yra suskirstytos į tris kategorijas, būtent aklas skylutes, palaidotas skylutes ir per skylutes.

Aklosios skylės yra spausdintos grandinės plokštės viršutiniame ir apatiniame paviršiuose ir turi tam tikrą gylį paviršiaus grandinės ir žemiau esančios vidinės grandinės sujungimui, o skylių gylis paprastai neviršija tam tikro santykio (diafragma).

Palaidota skylė reiškia jungties skylę, esančią spausdintos plokštės vidiniame sluoksnyje, kuri netaikoma lentos paviršiui. Aukščiau pateiktos dviejų tipų skylės yra vidiniame grandinės plokštės sluoksnyje, kurį prieš laminavimą užbaigia skylių formavimo procesas, o susidarant per skylę, keli vidiniai sluoksniai gali būti sutapti.

Trečiasis tipas vadinamas per skylutes, kurios praeina per visą plokštės plokštę ir gali būti naudojama norint pasiekti vidinį sujungimą arba kaip komponentų montavimo padėties nustatymo skylės. Kadangi proceso metu yra lengviau pasiekti skylę, o išlaidos yra mažesnės, didžioji dauguma spausdintų plokščių naudoja ja, o ne kitas dvi per skylutes. Šios skylės be specialių instrukcijų yra laikomos skylėmis.

Projektavimo požiūriu A Via daugiausia sudaro iš dviejų dalių, viena yra gręžimo angos vidurys, o kitas yra suvirinimo padėjimo sritis aplink gręžimo angą. Šių dviejų dalių dydis lemia VIA dydį.

Akivaizdu, kad greitaeigiu, didelio tankio PCB dizainu dizaineriai visada nori skylės, kad skylė būtų kuo mažesnė, kad būtų galima palikti daugiau laidų vietos, be to, kuo mažesnė „Via“, jos pačios parazitinė talpa yra mažesnė, labiau tinkama greitaeigių grandinėms.

Tačiau sumažinus „Via“ dydį, padidėja išlaidų padidėjimas, o skylės dydis negali būti sumažintas neribotą laiką, jį riboja gręžimo ir elektropliavimo technologija: kuo mažesnė skylė, tuo ilgiau reikia gręžti, tuo lengviau nukrypti nuo centro; Kai skylės gylis yra daugiau nei 6 kartus didesnis už skylės skersmenį, neįmanoma užtikrinti, kad skylės siena būtų vienodai padengta vario.

Pvz., Jei įprastos 6 sluoksnio PCB plokštės storis (per skylės gylį) yra 50 mln., Tada minimalus gręžimo skersmuo, kurį PCB gamintojai gali pateikti normaliomis sąlygomis, gali pasiekti tik 8 mln. Vykstant gręžimo lazeriui technologiją, gręžimo dydis taip pat gali būti mažesnis ir mažesnis, o skylės skersmuo paprastai yra mažesnis arba lygus 6 mln.

Mikroolai dažnai naudojami HDI (didelio tankio sujungimo struktūroje) konstrukcijoje, o mikroholų technologija gali leisti skylę tiesiogiai gręžti ant padėklo, o tai labai pagerina grandinės našumą ir taupo laidų vietą. VIA pasirodo kaip varžos nepertraukiamumas perdavimo linijoje, sukeldamas signalo atspindį. Paprastai lygiavertė skylės varža yra maždaug 12% mažesnė už perdavimo liniją, pavyzdžiui, 50 omų perdavimo linijos varža bus sumažinta 6 omais, kai ji praeis per skylę (konkrečiai ir VIA dydis, plokštės storis taip pat susijęs, o ne absoliutus sumažinimas).

Tačiau atspindys, kurį sukelia varžos nepertraukiamumas per VN, iš tikrųjų yra labai mažas, o jo atspindžio koeficientas yra tik:

(44-50)/(44 + 50) = 0,06

Problemos, kylančios iš VIA, yra labiau sutelktos į parazitinės talpos ir induktyvumo padarinius.

Per parazitinę talpą ir induktyvumą

Pačioje „Via“ yra parazitinė benamės talpa. Jei litavimo atsparumo zonos skersmuo ant išdėstyto sluoksnio yra D2, litavimo bloknotų skersmuo yra D1, PCB plokštės storis yra T, o substrato dielektrinė konstanta yra ε, parazitinė per skylės talpa yra maždaug:

C = 1,41εtd1/(d2-d1)

Pagrindinis parazitinės talpos poveikis grandinei yra prailginti signalo kilimo laiką ir sumažinti grandinės greitį.

Pvz., PCB, kurio storis yra 50 mln.

C = 1,41x4,4x0.050x0.020/(0,040-0.020) = 0,31pf

Šios talpos dalies sukelto kilimo laiko pokyčio kiekis yra maždaug:

T10-90 = 2,2c (Z0/2) = 2,2x0,31x (50/2) = 17,05ps

Iš šių verčių matyti, kad nors pakilimo uždelsimo naudingumas, kurį sukelia vienos parazitinė talpa, nėra labai akivaizdi, jei VIA kelis kartus naudojamas linijoje, norint perjungti sluoksnius, bus naudojamos kelios skylės, o dizainą reikia atidžiai įvertinti. Faktiniame dizaine parazitinė talpa gali būti sumažinta padidinus atstumą tarp skylės ir vario srities (anti-PAD) arba sumažinant pado skersmenį.

Projektuojant greitaeigių skaitmenines grandines, parazitinio induktyvumo padaryta žala dažnai yra didesnė už parazitinės talpos įtaką. Jos parazitinės serijos induktyvumas susilpnins apvedimo kondensatoriaus indėlį ir susilpnins visos galios sistemos filtravimo efektyvumą.

Mes galime naudoti šią empirinę formulę, kad tiesiog apskaičiuotume apytiksliai skylės parazitinį induktyvumą:

L = 5,08h [ln (4h/d) +1]

Kur L reiškia VIA induktyvumą, H yra VIA ilgis, o D yra centrinės skylės skersmuo. Iš formulės matyti, kad VIA skersmuo turi mažai įtakos induktyvumui, o VIA ilgis daro didžiausią įtaką induktyvumui. Vis dar naudojant aukščiau pateiktą pavyzdį, induktyvumą lauke galima apskaičiuoti taip:

L = 5,08x0,050 [ln (4x0,050/0,010) +1] = 1,015nh

Jei signalo kilimo laikas yra 1NS, tada jo lygiavertė varžos dydis yra:

Xl = πl/t10-90 = 3,19Ω

Tokios varžos negalima ignoruoti esant aukšto dažnio srovei per, ypač, atkreipkite dėmesį, kad aplinkkelio kondensatorius turi praeiti per dvi skylutes, kai jungiama galios sluoksnis ir formavimasis, kad skylės parazitinis induktyvumas būtų padaugintas.

Kaip naudotis VI?

Atlikę aukščiau pateiktą skylės parazitinių charakteristikų analizę, matome, kad greitaeigio PCB dizaino metu, atrodo, paprastos skylės dažnai sukelia didelį neigiamą poveikį grandinės projektavimui. Siekiant sumažinti neigiamą poveikį, kurį sukelia skylės parazitinis poveikis, dizainas gali būti kiek įmanoma:

Remdamiesi dviem išlaidų ir signalo kokybės aspektais, pasirinkite pagrįstą „Via“ dydžio dydį. Jei reikia, galite apsvarstyti galimybę naudoti skirtingų dydžių VIA, pavyzdžiui, dėl maitinimo šaltinio ar antžeminių vielos skylių, galite apsvarstyti galimybę naudoti didesnį dydį, kad sumažintumėte varžą, ir signalo laidams galite naudoti mažesnį VN. Žinoma, mažėjant VI

Dvi aukščiau aptartos formulės gali būti padarytos išvados, kad plonesnės PCB plokštės naudojimas yra palankus norint sumažinti du VIA parazitinius parametrus

PCB plokštės signalo laidai neturėtų būti kiek įmanoma keisti, tai yra, pabandykite nenaudoti nereikalingų viasų.

VIA reikia išgręžti į maitinimo šaltinio ir žemės kaiščius. Kuo trumpesnis švinas tarp kaiščių ir viaso, tuo geriau. Kelios skylės gali būti gręžiamos lygiagrečiai, kad būtų sumažintas lygiavertis induktyvumas.

Padėkite kai kuriuos įžemintus skylutes šalia signalo keitimo skylių, kad būtų artimiausia signalo kilpa. Ant PCB plokštės netgi galite įdėti keletą žemės skylių.

Didelio greičio PCB lentoms, turinčioms didelį tankį, galite apsvarstyti galimybę naudoti mikro skyles.