Aféierung vunVia-in-pad:

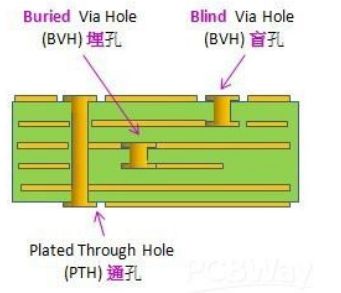

Sou ass et bekannt, datt VAIen d'VIIung (iwwer) opgedeelt ass, Lucis, Binzip a a verbrannt Studien.

De Besofzäit vun elektronesche Produkter, de Vii spillt eng vital Roll am Avelayer Interkonom-Primpf vu Dréift. Via-a-Bann gëtt wäit a klenge PCB a Bega benotzt (Kugel Gitter Array). Mat den indeelabléiser Entwécklung vun den Héich Dazitéit, BAD (Ball Gréng Array) an epd Chip Miniciologie gëtt d'Applikatioun vu VictoDiciologie ginn. D'Applikologie gëtt

Grale acks hunn vill Virwannen iwwer blann a begruewee viaszen gewisen

An. Gëeegent fir feine Pitch Bga.

An. Et ass bequem méi héije Dicht pcb ze bestätegen an ze spueren.

An. Besser thermesch Management.

An. Anti-niddereg Induktioun an aner Héichgeschwindegkeet Design.

An. Bitt eng flaach Uewerfläch fir Komponenten.

An. Reduzéiert PCB Regioun a weider ze verbesseren.

Aus deenen een Ze bestelle kënne ginn an der PAD déi bannen benotzt, déi meeschtens a PCB Designs benotzt ginn wéi Hëtztbewäert an héich Geschwindegkeet. Obwuel blann a burate Vakelesch Elementer erhéijen a spueren Raum op Pcbs, vias a Pads sinn ëmmer de beschte Choix fir Quisternotonen.

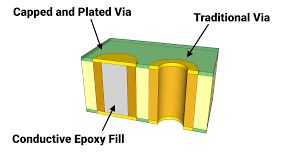

Mat engem zouverlässeg via Fëllung / Plating Caping Prozess, Via-in-in-in-in-in-in-in-anduercher Technik kann héich-Densy Pcbs ze produzéieren ouni Kierperhändler ze produzéieren Zousätzlech kann dëst zousätzlech Verbindungswand op BGA Designen ubidden.

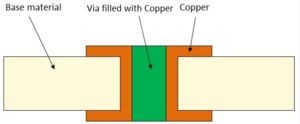

Et gi verschidde Füllmaterial fir d'Lach an der Teller, sëlwer Paste a Kupferpaste benotzt gi fir kondiv Materialien benotzt, an hält net fir net verflichte Materialien benotzt