D'Victoire ass ee vun de wichtege Komponenten vun der Multi-Schicht PCB, an d'Käschte fir ze billen fir 30% bis 40% vun de Käschte vum PCB Board. Leet einfach, all Lach um PCB kann eng via geruff ginn.

De Basiskonzept vun der via:

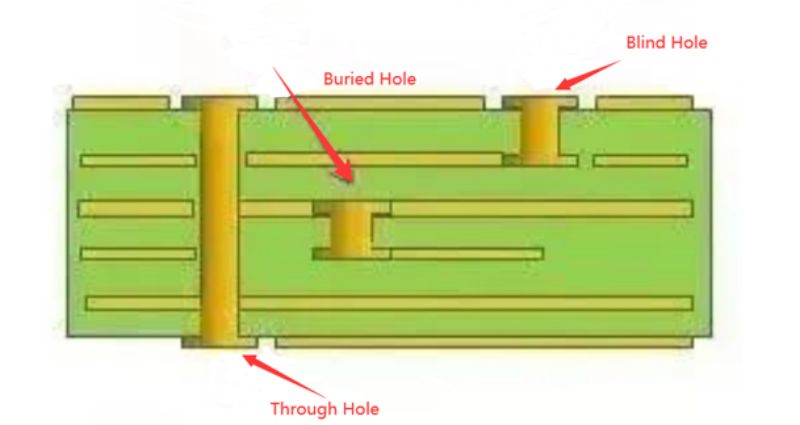

Aus der Siichtsplaz vun der Funktioun, d'Via kann an zwou Kategorien agedeelt ginn: een gëtt als elektresch Verbindung tëscht de Schichten benotzt, an deen aneren gëtt als Fixing vum Apparat benotzt. Wann aus dem Prozess sinn, ginn dës Lächer allgemeng an dräi Kategorien, nämlech Lächer, verbrennt Lächer an duerch Lächer.

Dräi hu Harmel langen op uewen an Ënnerflësseplacmen vun engem Drécke Cuccit Board an invitéiert eng Verbindung vum Recycling an den Zeittefall an den Zerstöl bei de Buedemskurch.

Déi begruewe Hakeren uginn op ännert et Iwwrechelschmaaltmolfplaz, dat net op d'Uewerfaarfrenstum vu Bours bestëmmt. Déi vun zwee Aarte vu Klänglechkeeten sinn am Terland Schied vum Terre CrereCuitsplang, an deem wéinegen nohaltege Feeler vum duerchgefouert, an d'Formatioun vum duerchgefouert iwwer hinne iwwer zwee Aarte vu Lächer. An der Zoll Schichten vum Terre Crereol Maltightsprozess deen an d'Formatioun vum duerch duerchgefouert gouf.

Déi drëttaart genannt, wéieng Lächer genannt ginn, wéi och duerch dee ganze Figur Board passéiert a ka benotzt ginn fir intern Interkonomung ze erreechen Well dat duerch d'Käschte méi einfach gëtt fir am Prozess ze erreechen an d'Käschte méi niddereg ass, déi grouss Majoritéit vun gedréckte Circuiten benotzt, anstatt déi aner zwee duerch Lächer. Déi folgend Lächer, ouni Spezial Instruktioun gi wéinst Holeuren ugesinn.

Reim éischte Punkte vun den Issgott, déi haaptsächlech vun zwee Deeler zesummegesat ginn, ass deen domadder vum Buerstad, an den anere fuedridden bei den Splécken Haus. D'Gréisst vun dësen zwee Deeler bestëmmt d'Gréisst vun iwwer.

An elo organisenz sinn, an enger héijer Geschwindegkeet, héichstätzungszspëtzungen ëmmer d'Läsch méi kleng, sou datt méi vill Fra, esou eng Plaz bleift eleng loossen. Zousätzlech duerch eng Plaz bleift aus, anerer sinn, och ëmmer erëm

Wéi och ëmmer, d'Ruch vun der Schoul bréngt ëmmer méi sprenger Floss, wat d'Gréisst vum Louis net méi fréiere reduzéiert ass; Wann d'Déift vum Lach ass ass méi wéi 6 Mol den Duerchmiesser vum Lach, ass et onméiglech ze garantéieren datt d'Lachmauer, déi mat Kupfer mat Kupfer gesat goufen.

Zënterhier, soss ass d'Dickheet (duerch Kolf) vun engem normale 6-Schichten PCB Board Zesummeele gëtt d'Gréisst vun de Coursen drénken, der Gréisst vun de Flaugeröff net méi manner sinn, ass vill Microhohe.

D'Mikholes ginn dacks am HDI benotzt, an HDE DONSEY DONSECONNT ZECTIONE) Design, a Microhole Technologie erlaben, déi d'Lach ass an der Pad, déi d'Lach an der Padh identifizéiert gëtt. D'Vize erschéngt als Breakpoint vun der Impedanzverhandlung op der Iwwerdroungsgrenz, verursaacht eng Reflexioun vum Signal. Allgemeng sin den Equili vum Lach fir 12% manner wéi 12% mannerberäicher,.

Wéi och ëmmer, d'Reflexioun verursaacht duerch d'Impaktular-Diskontinuitéit via ass tatsächlech ganz kleng, an d'Reflexiounszoustand ass nëmmen:

(44-50) / (44 + 50) = 0.06

D'Problemer entstoe vu via si méi konzentréiert op d'Effekter vum parasiteschen Fäegkeet.

Via seng parasitesch Fäegkeet an Induktioun

Et gëtt eng parasitesch Stammkraaftverstand an der via sech selwer. Wann den Duerchdiesser vun der läscher Resistenzzon vum geleeëntleche Schicht ass, ass den Duerchmiesser vun de Solterpazter vum Sold Pad vum Décker, an den Décker vum Diglerbetrikt ass d1, an d'Substrat ass ongeféier: den Duerchschnëtt ass ongeféier:

C = 1.41εtd1 / (D2-D1)

Den Haaptattack vu dem parasitescher Fäegkeet ass um Crecuit an d'Signal ofzepassen a reduzéieren d'Geschwindeg vum Kreit.

Zum Beispill fir e PCB mat enger Dickéierung vun 50m, wann d'Duerchbau vun der Ofstruktur ass, da wäerte sech 10millen sinn, also vu Daterrigerung (den Duerchmiesserwereen vun den Diesser Droen ass véiermant, da kënne mir Troicken aus der Sabrümererwernisser féieren "

C = 1.41x4.4x00.00.020 / (0.040-0200.00) = 0.31pf

De Betrag vun der Erhéijung vun der Erhéijung vun dësem Deel vun dësem Deel vun der Kapazitéit ass ongeféier:

T10-90 = 2.2C (z0 / 2) = 2.2x0,31x (50/2) = 17.05ps

Si ka vun dëse Wäerter gesi ginn, déi och den Utilitéite vun de Parasitikanz vun enger anerer Meenung no ginn. Am aktuellen Design, huet de paraseschen Fäegkeete ka ginn duerch d'Distanz tëscht dem Lach an dem Koppel Beräich (Anti Pad) oder an Anti-Pad) oder Antiewent vum Pad.

Am Design vun héijer Geschwindegkeet digital Circuiten, de Schued, dee Schued verursaacht duerch parasitesch Induktioun ass dacks méi grouss wéi den Afloss vun der parasititescher Fäegkeet. Seng Parastikalesch Serie Engidatioun, déi de Kontext vum Rentwerterfaritege vir mat onsekréien.

Bei desem Formaterial Generellegkeet vun der zoustung vum figer Formula Et huet einfach déi paragsins offiziell vun enger duerch ze berechent vun engem duerch-luconimimimatioun ze kréien:

L = 5.08h [ln (4h / d) +1]

Hei wou ech an deen anzen organiséiere bezetzten, ass et d'Längt vun iwwer d'Längt vun dran, an d Duerchmiesser vum Centternach. Et ka aus der Formula gesinn, datt den Duerchmiesser vun der via e klengen Afloss op den Indiewë vun der Via huet, wärend d'Längt vun der viaer Octizitéit op der Induktioun huet. Trotzdem benotzt den uewe genannte Beispill, d'Out-Liter Induktioun ka berechent ginn als:

L = 5.08x0.050 [ln (4x0.050 / 0.010) +1] = 1.015nh

Wann d'Erhéijung vun der Signal 1s ass, dann ass seng gläichwäerteg Belaaschtungsgréisst ass:

Xl = πl / t10-90 = 3.19.ω

Sougedéierenduerch d'Formatioun net gebuer, wat d'Präsenzin um Aktioun mat enger Héich-Frequenz duerchfuerdert, muss den Pentre geleeënt, well d'paracatsal Induktioun vum Leschejeten, sou datt déi paradizinesche Projet kéinen.

Wéi benotzen ech iwwer?

Duerch den Uestrendrée vun Ufank vum Paragitesche Charakteristike vum Gesiichts kann mir dat am Halschte Sessens pro Zweck bréngen, aen Attitude huet vill Auswierkunge grouss negativ Weis wéi den Design vum Katendek. Fir déi geséchter Effekter déi nom parasitesche Effekt vum Lach verursaache reduzéieren, kann den Design méi wéi méiglech ugaang sinn:

Vun deenen zwee Aspekter vu Käschten a Signalqualitéit, wielt eng ugemoossen Gréisst vun der via Gréisst. Wann néideg kënnt, kënnt Dir verschidde Sainden vun der Via Life benotze kënnen, sou wéi fir d'Energiebetreiung oder Terrain Lächer, Dir kënnt mat enger méi grousser Gréisst benotzen, a fir Signalgrupp ze reduzéieren, a fir Signaldirung ze reduzéieren, a fir Signalwirmung ze reduzéieren, a fir eng onméiglechkeeten ze maachen Natierlech, wéi d'Gréisst vun der via erof geet, gëtt déi entspriechend Käschte och erop

Déi zwee Formelen hunn hei uewen diskutéiert ginn kann ofgeschloss ginn datt d'Benotzung vun engem méi dënnen PCB Board gefälscht ass fir déi zwee parasitesch Parameteren vun der via ze reduzéieren

D'Signal Drot um PCB BLANCE WANN NET ECH NET GEMAACHT, DAT AS SIEN, net onnéideg onnéideg Via ze benotzen.

D'LASAS muss an d'Pneu vun der Energieverolunung an de Buedem geborf ginn. De Krerung setierkelt sech d'es tëscht de Pricken an dem Viiff, dat besser. Multiple Lächer kënne parallel gedronk ginn fir déi gläichwäerteg Induktioun ze reduzéieren.

Setzt e puer op-Lächer no bei der Verloschter vun der Signal Ännerung fir déi nooste Loop fir d'Signal ze bidden. Dir kënnt och e puer iwwerschësseg Buedem Lächer um PCB Board setzen.

Fir Héichgeschwindegkeet PCB Brieder mat héijer Dicht, kënnt Dir mat Mikro-Lächer betruechten.