ვია არის მრავალფენიანი PCB-ის ერთ-ერთი მნიშვნელოვანი კომპონენტი და ბურღვის ღირებულება ჩვეულებრივ შეადგენს PCB დაფის ღირებულების 30%-დან 40%-მდე. მარტივად რომ ვთქვათ, PCB-ზე ყველა ხვრელს შეიძლება ეწოდოს via.

Via-ს ძირითადი კონცეფცია:

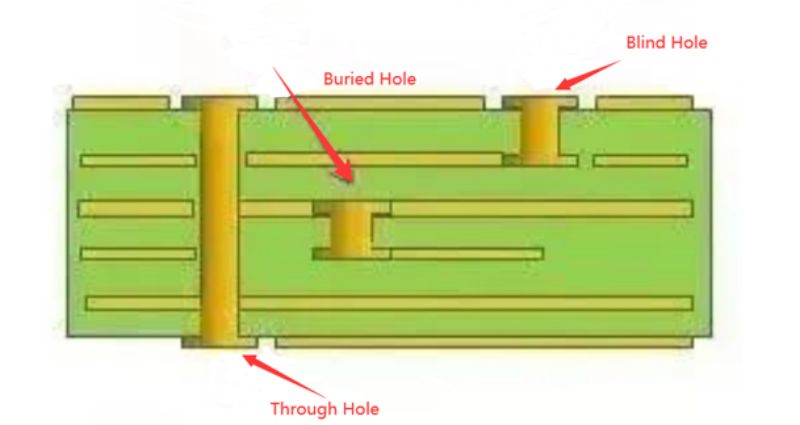

ფუნქციის თვალსაზრისით, ვია შეიძლება დაიყოს ორ კატეგორიად: ერთი გამოიყენება როგორც ელექტრული კავშირი ფენებს შორის, ხოლო მეორე გამოიყენება როგორც მოწყობილობის დამაგრება ან პოზიციონირება. თუ პროცესიდან, ეს ხვრელები ზოგადად იყოფა სამ კატეგორიად, კერძოდ, ბრმა ხვრელები, დამარხული ხვრელები და ნახვრეტები.

ბრმა ხვრელები განლაგებულია ბეჭდური მიკროსქემის დაფის ზედა და ქვედა ზედაპირებზე და აქვთ გარკვეული სიღრმე ზედაპირული მიკროსქემისა და ქვევით შიდა წრედის შესაერთებლად, ხოლო ხვრელების სიღრმე ჩვეულებრივ არ აღემატება გარკვეულ თანაფარდობას (დიფრაგმას).

ჩამარხული ხვრელი ეხება შეერთების ხვრელს, რომელიც მდებარეობს ბეჭდური მიკროსქემის დაფის შიდა ფენაში, რომელიც არ ვრცელდება დაფის ზედაპირზე. ზემოაღნიშნული ორი ტიპის ხვრელები განლაგებულია მიკროსქემის დაფის შიდა ფენაში, რომელიც სრულდება ლამინირების წინ ხვრელების ჩამოსხმის პროცესით და რამდენიმე შიდა ფენა შეიძლება გადახურული იყოს გამტარი ხვრელის ფორმირებისას.

მესამე ტიპს ეწოდება გამტარი ხვრელები, რომლებიც გადის მთელ მიკროსქემის დაფაზე და შეიძლება გამოყენებულ იქნას შიდა ურთიერთკავშირის მისაღწევად ან კომპონენტების სამონტაჟო პოზიციონირების ხვრელებად. იმის გამო, რომ გამჭოლი ხვრელი უფრო ადვილად მიიღწევა პროცესში და ღირებულება უფრო დაბალია, ბეჭდური მიკროსქემის დაფების აბსოლუტური უმრავლესობა იყენებს მას, ვიდრე დანარჩენ ორს. შემდეგი ხვრელები, სპეციალური ინსტრუქციის გარეშე, განიხილება, როგორც ნახვრეტები.

დიზაინის თვალსაზრისით, ვია ძირითადად შედგება ორი ნაწილისგან, ერთი არის საბურღი ხვრელის შუა ნაწილი, ხოლო მეორე არის საბურღი ხვრელის გარშემო შედუღების ბალიშის არე. ამ ორი ნაწილის ზომა განსაზღვრავს ვიას ზომას.

ცხადია, მაღალსიჩქარიანი, მაღალი სიმკვრივის PCB დიზაინში, დიზაინერებს ყოველთვის უნდათ, რომ ხვრელი რაც შეიძლება პატარა იყოს, რათა მეტი გაყვანილობის ადგილი დარჩეს, გარდა ამისა, რაც უფრო მცირეა ვია, მისი საკუთარი პარაზიტული ტევადობა უფრო მცირეა, უფრო შესაფერისი. მაღალსიჩქარიანი სქემებისთვის.

თუმცა, ვიას ზომის შემცირება ასევე იწვევს ხარჯების ზრდას და ხვრელის ზომა განუსაზღვრელი ვადით არ შეიძლება შემცირდეს, ის შემოიფარგლება ბურღვისა და ელექტრული ტექნოლოგიით: რაც უფრო პატარაა ხვრელი, მით უფრო გრძელია ბურღვა, მით უფრო ადვილია. არის ცენტრიდან გადახრა; როდესაც ხვრელის სიღრმე 6-ჯერ აღემატება ხვრელის დიამეტრს, შეუძლებელია იმის უზრუნველყოფა, რომ ხვრელის კედელი შეიძლება ერთნაირად იყოს მოოქროვილი სპილენძით.

მაგალითად, თუ ჩვეულებრივი 6-ფენიანი PCB დაფის სისქე (ხვრელის სიღრმეში) არის 50 მილი, მაშინ ბურღვის მინიმალური დიამეტრი, რომელიც PCB მწარმოებლებს შეუძლიათ უზრუნველყონ ნორმალურ პირობებში, შეიძლება მხოლოდ 8 მილ-ს მიაღწიოს. ლაზერული ბურღვის ტექნოლოგიის განვითარებით, ბურღვის ზომა ასევე შეიძლება იყოს უფრო და უფრო მცირე, ხოლო ხვრელის დიამეტრი ზოგადად 6 Mils-ზე ნაკლები ან ტოლია, ჩვენ გვეძახიან მიკროხვრელებს.

მიკროხვრელებს ხშირად იყენებენ HDI (მაღალი სიმკვრივის ურთიერთდაკავშირების სტრუქტურის) დიზაინში და მიკროხვრელების ტექნოლოგია საშუალებას აძლევს ხვრელს პირდაპირ გაბურღოს ბალიშზე, რაც მნიშვნელოვნად აუმჯობესებს მიკროსქემის მუშაობას და დაზოგავს გაყვანილობის ადგილს. Via ჩნდება, როგორც წინაღობის შეწყვეტის წერტილი გადამცემ ხაზზე, რაც იწვევს სიგნალის ასახვას. ზოგადად, ხვრელის ეკვივალენტური წინაღობა დაახლოებით 12% -ით დაბალია, ვიდრე გადამცემი ხაზი, მაგალითად, 50 ohms გადამცემი ხაზის წინაღობა შემცირდება 6 ohms-ით, როდესაც ის გაივლის ხვრელში (კონკრეტულად და მილის ზომა, ფირფიტის სისქე ასევე დაკავშირებულია და არა აბსოლუტური შემცირება).

თუმცა, წინაღობის შეწყვეტით გამოწვეული ანარეკლი რეალურად ძალიან მცირეა და მისი ასახვის კოეფიციენტი არის მხოლოდ:

(44-50)/(44 + 50) = 0.06

ვიასგან წარმოქმნილი პრობლემები უფრო კონცენტრირებულია პარაზიტული ტევადობისა და ინდუქციურობის ეფექტებზე.

Via-ს პარაზიტული ტევადობა და ინდუქციურობა

თავად ვიაში არის პარაზიტული მაწანწალა ტევადობა. თუ დაფენილ ფენაზე შედუღების წინააღმდეგობის ზონის დიამეტრი არის D2, შედუღების ბალიშის დიამეტრი არის D1, PCB დაფის სისქე არის T და სუბსტრატის დიელექტრიკული მუდმივია ε, გამავალი ხვრელის პარაზიტული ტევადობა. არის დაახლოებით:

C=1.41εTD1/(D2-D1)

პარაზიტული ტევადობის ძირითადი ეფექტი წრედზე არის სიგნალის აწევის დროის გახანგრძლივება და მიკროსქემის სიჩქარის შემცირება.

მაგალითად, PCB-სთვის, რომლის სისქეა 50 მილი, თუ საბურველის დიამეტრი არის 20 მილი (საბურღი ხვრელის დიამეტრი 10 მილი) და შედუღების წინააღმდეგობის ზონის დიამეტრი არის 40 მილი, მაშინ შეგვიძლია მივახლოვოთ პარაზიტული ტევადობა. via ზემოთ ფორმულით:

C=1.41x4.4x0.050x0.020/(0.040-0.020)=0.31pF

ტევადობის ამ ნაწილით გამოწვეული აწევის დროის ცვლილების რაოდენობა არის დაახლოებით:

T10-90=2.2C(Z0/2)=2.2x0.31x(50/2)=17.05ps

ამ მნიშვნელობებიდან ჩანს, რომ მიუხედავად იმისა, რომ აწევის დაყოვნების სარგებლობა, რომელიც გამოწვეულია ერთი გამშვების პარაზიტული ტევადობით, არც თუ ისე აშკარაა, თუ ვია ხაზში რამდენჯერმე გამოიყენება ფენებს შორის გადასართავად, გამოყენებული იქნება მრავალი ხვრელი, და დიზაინი ყურადღებით უნდა იქნას განხილული. რეალურ დიზაინში, პარაზიტული ტევადობა შეიძლება შემცირდეს ხვრელსა და სპილენძის არეს შორის მანძილის გაზრდით (Anti-pad) ან ბალიშის დიამეტრის შემცირებით.

მაღალსიჩქარიანი ციფრული სქემების დიზაინში, პარაზიტული ინდუქციით გამოწვეული ზიანი ხშირად უფრო მეტია, ვიდრე პარაზიტული ტევადობის გავლენა. მისი პარაზიტული სერიის ინდუქციურობა შეასუსტებს შემოვლითი კონდენსატორის წვლილს და შეასუსტებს მთელი ენერგეტიკული სისტემის ფილტრაციის ეფექტურობას.

ჩვენ შეგვიძლია გამოვიყენოთ შემდეგი ემპირიული ფორმულა, რომ უბრალოდ გამოვთვალოთ ნახვრეტის მიახლოების პარაზიტული ინდუქციურობა:

L=5.08სთ[ln(4სთ/დ)+1]

სადაც L ეხება via-ს ინდუქციურობას, h არის via-ს სიგრძე და d არის ცენტრალური ხვრელის დიამეტრი. ფორმულიდან ჩანს, რომ ვიას დიამეტრი მცირე გავლენას ახდენს ინდუქციურობაზე, ხოლო ვიას სიგრძე ყველაზე დიდ გავლენას ახდენს ინდუქციურობაზე. მიუხედავად ამისა, ზემოთ მოყვანილი მაგალითის გამოყენებით, ხვრელიდან გამოსული ინდუქციურობა შეიძლება გამოითვალოს შემდეგნაირად:

L=5.08x0.050[ln(4x0.050/0.010)+1]=1.015nH

თუ სიგნალის აწევის დრო არის 1 წმ, მაშინ მისი ეკვივალენტური წინაღობის ზომაა:

XL=πL/T10-90=3.19Ω

ასეთი წინაღობა არ შეიძლება იგნორირებული იყოს მაღალი სიხშირის დენის არსებობისას, კერძოდ, გაითვალისწინეთ, რომ დენის ფენისა და ფორმირების შეერთებისას შემოვლითი კონდენსატორი უნდა გაიაროს ორ ხვრელში, რათა გამრავლდეს ხვრელის პარაზიტული ინდუქცია.

როგორ გამოვიყენოთ via?

ხვრელის პარაზიტული მახასიათებლების ზემოაღნიშნული ანალიზის საშუალებით, ჩვენ ვხედავთ, რომ მაღალსიჩქარიანი PCB დიზაინის დროს, ერთი შეხედვით მარტივი ხვრელები ხშირად დიდ უარყოფით ეფექტებს მოაქვს მიკროსქემის დიზაინზე. ხვრელის პარაზიტული ეფექტით გამოწვეული უარყოფითი ეფექტების შესამცირებლად, დიზაინი მაქსიმალურად შეიძლება იყოს:

ღირებულებისა და სიგნალის ხარისხის ორი ასპექტიდან, აირჩიეთ ვია ზომის გონივრული ზომა. საჭიროების შემთხვევაში, შეგიძლიათ გამოიყენოთ სხვადასხვა ზომის ვიზები, როგორიცაა ელექტრომომარაგების ან დამიწების მავთულის ხვრელების გამოყენება, შეგიძლიათ გამოიყენოთ უფრო დიდი ზომის წინაღობის შესამცირებლად, ხოლო სიგნალის გაყვანილობისთვის შეგიძლიათ გამოიყენოთ უფრო მცირე ვიზა. რა თქმა უნდა, ვიას ზომის შემცირებით, შესაბამისი ღირებულებაც გაიზრდება

ზემოთ განხილული ორი ფორმულიდან შეიძლება დავასკვნათ, რომ უფრო თხელი PCB დაფის გამოყენება ხელს უწყობს ვია-ს ორი პარაზიტული პარამეტრის შემცირებას.

PCB დაფაზე სიგნალის გაყვანილობა მაქსიმალურად არ უნდა შეიცვალოს, ანუ შეეცადეთ არ გამოიყენოთ ზედმეტი ვიზები.

ვიზები უნდა იყოს გაბურღული ელექტრომომარაგების და გრუნტის ქინძისთავებში. რაც უფრო მოკლეა მანძილი ქინძისთავებსა და ვიზებს შორის, მით უკეთესი. რამდენიმე ხვრელის გაბურღვა შესაძლებელია პარალელურად, რათა შემცირდეს ეკვივალენტური ინდუქციურობა.

მოათავსეთ რამდენიმე დასაბუთებული ნახვრეტი სიგნალის ცვლილების ღიობების მახლობლად, რათა უზრუნველყოთ სიგნალის უახლოესი მარყუჟი. თქვენ შეგიძლიათ კიდევ მოათავსოთ ჭარბი გრუნტის ხვრელები PCB დაფაზე.

მაღალი სიჩქარის PCB დაფებისთვის, მაღალი სიმკვრივით, შეგიძლიათ გამოიყენოთ მიკრო ხვრელების გამოყენება.