Yen kapasitansi interlayer ora cukup gedhe, kolom listrik bakal disebarake liwat area papan sing relatif gedhe, supaya impedansi interlayer suda lan arus bali bisa bali menyang lapisan ndhuwur. Ing kasus iki, lapangan sing diasilake sinyal iki bisa ngganggu lapangan sinyal lapisan sing ganti cedhak. Iki dudu apa sing kita ngarepake. Sayange, ing papan 4-lapisan 0,062 inci, lapisan kasebut adoh lan kapasitansi interlayer cilik.

Nalika wiring diganti saka lapisan 1 kanggo Layer 4 utawa kosok balene, banjur bakal mimpin masalah iki ditampilake minangka gambar

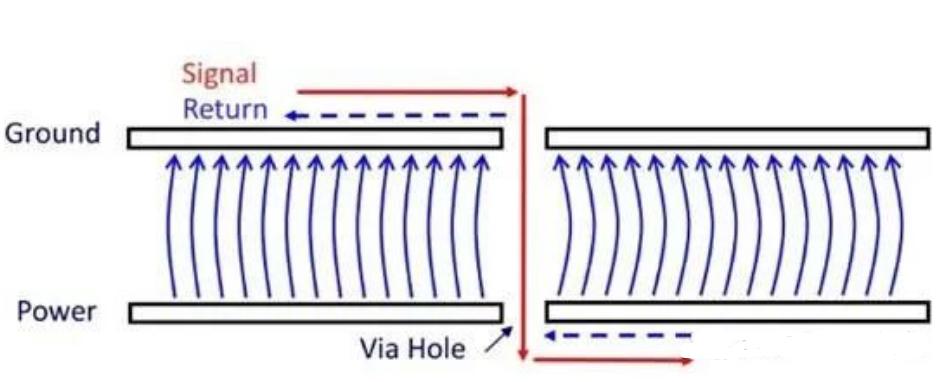

Diagram nuduhake yen sinyal trek saka lapisan 1 kanggo lapisan 4 (garis abang), arus bali uga kudu ngganti bidang (garis biru). Yen frekuensi sinyal cukup dhuwur lan pesawat cedhak, arus bali bisa mili liwat kapasitansi interlayer sing ana ing antarane lapisan lemah lan lapisan daya. Nanging, amarga ora ana sambungan konduktif langsung kanggo arus bali, jalur bali diselani, lan kita bisa mikir yen gangguan iki minangka impedansi antarane pesawat sing ditampilake ing gambar ing ngisor iki.

Yen kapasitansi interlayer ora cukup gedhe, kolom listrik bakal disebarake liwat area papan sing relatif gedhe, supaya impedansi interlayer suda lan arus bali bisa bali menyang lapisan ndhuwur. Ing kasus iki, lapangan sing diasilake sinyal iki bisa ngganggu lapangan sinyal lapisan sing ganti cedhak. Iki dudu apa sing kita ngarepake. Sayange, ing Papan 4-lapisan 0,062 inci, lapisan adoh loro (paling 0,020 inci), lan kapasitansi interlayer cilik. Akibaté, gangguan medan listrik sing diterangake ing ndhuwur dumadi. Iki bisa uga ora nyebabake masalah integritas sinyal, nanging mesthi bakal nggawe EMI luwih akeh. Mulane, nalika nggunakake kaskade, kita ora ngganti lapisan, utamane kanggo sinyal frekuensi dhuwur kayata jam.

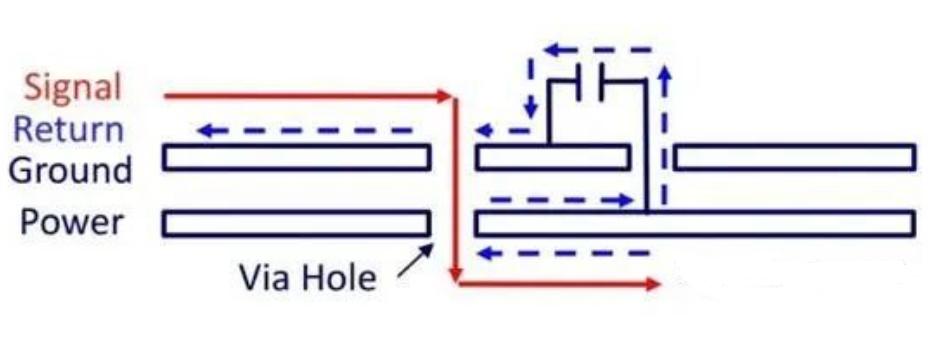

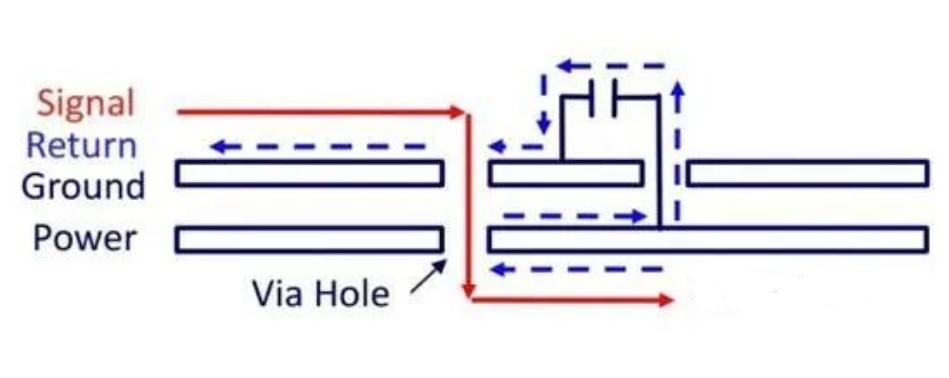

Praktek umum kanggo nambah kapasitor decoupling cedhak bolongan pass transisi kanggo ngurangi impedansi sing dialami dening arus bali sing ditampilake ing gambar ing ngisor iki. Nanging, kapasitor decoupling iki ora efektif kanggo sinyal VHF amarga frekuensi swa-resonansi sing kurang. Kanggo sinyal AC karo frekuensi luwih saka 200-300 MHz, kita ora bisa gumantung ing kapasitor decoupling kanggo nggawe dalan bali impedansi kurang. Mulane, kita butuh kapasitor decoupling (kanggo ngisor 200-300 MHz) lan kapasitor interboard sing relatif gedhe kanggo frekuensi sing luwih dhuwur.

Masalah iki bisa nyingkiri kanthi ora ngganti lapisan sinyal tombol. Nanging, kapasitansi interboard cilik saka papan papat-lapisan ndadékaké kanggo masalah serius liyane: transmisi daya. Jam digital ics biasane mbutuhake arus sumber daya transien gedhe. Nalika munggah / tiba wektu output IC sudo, kita kudu ngirim energi ing tingkat sing luwih dhuwur. Kanggo nyedhiyani sumber daya, kita biasane nyeleh kapasitor decoupling banget cedhak saben IC logika. Nanging, ana masalah: nalika kita ngluwihi frekuensi resonansi dhewe, kapasitor decoupling ora bisa nyimpen lan nransfer energi kanthi efisien, amarga ing frekuensi kasebut kapasitor bakal tumindak kaya induktor.

Wiwit paling ics saiki wis cepet munggah / tiba kaping (bab 500 ps), kita kudu struktur decoupling tambahan karo frekuensi poto-resonansi luwih saka kapasitor decoupling. Kapasitas interlayer saka papan sirkuit bisa dadi struktur decoupling efektif, kasedhiya yen lapisan cukup cedhak saben liyane kanggo nyedhiyani kapasitansi cekap. Mulane, saliyane kapasitor decoupling sing umum digunakake, kita luwih seneng nggunakake lapisan daya lan lapisan lemah sing rapet kanggo nyedhiyakake daya sementara kanggo ics digital.

Wigati dicathet menawa amarga proses manufaktur papan sirkuit umum, kita biasane ora duwe insulator tipis ing antarane lapisan kaping pindho lan katelu saka papan papat lapisan. Papan papat lapisan kanthi insulator tipis ing antarane lapisan kaping pindho lan katelu bisa larang luwih akeh tinimbang papan papat lapisan konvensional.