Via adalah salah satu komponen penting PCB multi-layer, dan biaya pengeboran biasanya menyumbang 30% hingga 40% dari biaya papan PCB. Sederhananya, setiap lubang di PCB dapat disebut via.

Konsep dasar via:

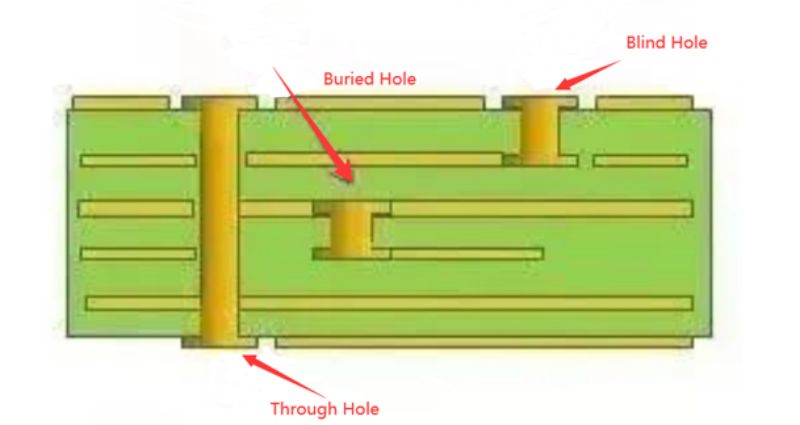

Dari sudut pandang fungsi, via dapat dibagi menjadi dua kategori: satu digunakan sebagai hubungan listrik antara lapisan, dan yang lainnya digunakan sebagai pemasangan atau penentuan posisi perangkat. Jika dari proses tersebut, lubang -lubang ini umumnya dibagi menjadi tiga kategori, yaitu lubang buta, lubang terkubur dan melalui lubang.

Lubang buta terletak di permukaan atas dan bawah papan sirkuit cetak dan memiliki kedalaman tertentu untuk koneksi sirkuit permukaan dan sirkuit dalam di bawah, dan kedalaman lubang biasanya tidak melebihi rasio tertentu (aperture).

Lubang yang terkubur mengacu pada lubang koneksi yang terletak di lapisan dalam papan sirkuit cetak, yang tidak meluas ke permukaan papan. Dua jenis lubang di atas terletak di lapisan dalam papan sirkuit, yang diselesaikan oleh proses cetakan melalui lubang sebelum laminasi, dan beberapa lapisan dalam mungkin tumpang tindih selama pembentukan lubang melalui.

Jenis ketiga disebut melalui lubang, yang melewati seluruh papan sirkuit dan dapat digunakan untuk mencapai interkoneksi internal atau sebagai lubang penentuan posisi pemasangan untuk komponen. Karena lubang melalui lebih mudah dicapai dalam proses dan biayanya lebih rendah, sebagian besar papan sirkuit cetak menggunakannya, daripada dua lainnya melalui lubang. Lubang -lubang berikut, tanpa instruksi khusus, dianggap melalui lubang.

Dari sudut pandang desain, via terutama terdiri dari dua bagian, satu adalah tengah lubang pengeboran, dan yang lainnya adalah area bantalan pengelasan di sekitar lubang pengeboran. Ukuran kedua bagian ini menentukan ukuran via.

Jelas, dalam desain PCB berkecepatan tinggi, kepadatan tinggi, para desainer selalu menginginkan lubang sekecil mungkin, sehingga lebih banyak ruang kabel dapat dibiarkan, di samping itu, semakin kecil via, kapasitansi parasitnya sendiri lebih kecil, lebih cocok untuk sirkuit berkecepatan tinggi.

Namun, pengurangan ukuran melalui juga membawa peningkatan biaya, dan ukuran lubang tidak dapat dikurangi tanpa batas waktu, dibatasi oleh teknologi pengeboran dan elektroplating: semakin kecil lubang, semakin lama pengeboran, semakin mudah untuk menyimpang dari pusat; Ketika kedalaman lubang lebih dari 6 kali diameter lubang, tidak mungkin untuk memastikan bahwa dinding lubang dapat dilapisi secara seragam dengan tembaga.

Misalnya, jika ketebalan (melalui kedalaman lubang) dari papan PCB 6-lapis normal adalah 50 juta, maka diameter pengeboran minimum yang dapat disediakan oleh produsen PCB dalam kondisi normal hanya dapat mencapai 8mil. Dengan pengembangan teknologi pengeboran laser, ukuran pengeboran juga bisa lebih kecil dan lebih kecil, dan diameter lubang umumnya kurang dari atau sama dengan 6 juta, kami disebut lubang mikro.

Lubang mikro sering digunakan dalam desain HDI (struktur interkoneksi kepadatan tinggi), dan teknologi lubang mikro dapat memungkinkan lubang dibor secara langsung pada pad, yang sangat meningkatkan kinerja sirkuit dan menghemat ruang kabel. Via muncul sebagai breakpoint diskontinuitas impedansi pada saluran transmisi, menyebabkan refleksi sinyal. Secara umum, impedansi yang setara dari lubang adalah sekitar 12% lebih rendah dari saluran transmisi, misalnya, impedansi saluran transmisi 50 ohm akan dikurangi 6 ohm ketika melewati lubang (khusus dan ukuran via, ketebalan pelat juga terkait, bukan reduksi absolut).

Namun, refleksi yang disebabkan oleh impedansi diskontinuitas via sebenarnya sangat kecil, dan koefisien refleksinya hanya:

(44-50)/(44 + 50) = 0,06

Masalah yang timbul dari via lebih terkonsentrasi pada efek kapasitansi dan induktansi parasit.

Kapasitansi dan induktansi parasit via

Ada kapasitansi liar parasit di Via sendiri. Jika diameter zona resistensi solder pada lapisan yang diletakkan adalah D2, diameter bantalan solder adalah D1, ketebalan papan PCB adalah T, dan konstanta dielektrik substrat adalah ε, kapasitansi parasit dari lubang melalui kira -kira:

C = 1.41εTD1/(D2-D1)

Efek utama dari kapasitansi parasit pada sirkuit adalah memperpanjang waktu kenaikan sinyal dan mengurangi kecepatan sirkuit.

Misalnya, untuk PCB dengan ketebalan 50mil, jika diameter pad via adalah 20mil (diameter lubang pengeboran adalah 10 juta) dan diameter zona resistensi solder adalah 40 juta, maka kita dapat mendekati kapasitansi parasit via dengan formula di atas:

C = 1.41x4.4x0.050x0.020/(0.040-0.020) = 0.31pf

Jumlah perubahan waktu kenaikan yang disebabkan oleh bagian kapasitansi ini kira -kira:

T10-90 = 2.2C (Z0/2) = 2.2x0.31x (50/2) = 17.05ps

Dapat dilihat dari nilai -nilai ini bahwa meskipun kegunaan penundaan kenaikan yang disebabkan oleh kapasitansi parasit dari satu via tidak terlalu jelas, jika via digunakan beberapa kali dalam jalur untuk beralih di antara lapisan, beberapa lubang akan digunakan, dan desain harus dipertimbangkan dengan hati -hati. Dalam desain yang sebenarnya, kapasitansi parasit dapat dikurangi dengan meningkatkan jarak antara lubang dan area tembaga (anti-pad) atau mengurangi diameter pad.

Dalam desain sirkuit digital berkecepatan tinggi, kerusakan yang disebabkan oleh induktansi parasit seringkali lebih besar dari pengaruh kapasitansi parasit. Induktansi seri parasitnya akan melemahkan kontribusi kapasitor bypass dan melemahkan efektivitas penyaringan seluruh sistem daya.

Kita dapat menggunakan formula empiris berikut untuk hanya menghitung induktansi parasit dari pendekatan melalui lubang:

L = 5.08H [LN (4H/D) +1]

Di mana L mengacu pada induktansi via, h adalah panjang via, dan d adalah diameter lubang pusat. Dapat dilihat dari formula bahwa diameter via memiliki sedikit pengaruh pada induktansi, sedangkan panjang via memiliki pengaruh terbesar pada induktansi. Masih menggunakan contoh di atas, induktansi di luar lubang dapat dihitung sebagai:

L = 5.08x0.050 [LN (4x0.050/0.010) +1] = 1.015nh

Jika kenaikan waktu sinyal adalah 1NS, maka ukuran impedansinya yang setara adalah:

Xl = πl/t10-90 = 3.19Ω

Impedansi seperti itu tidak dapat diabaikan dengan adanya arus frekuensi tinggi melalui, khususnya, perhatikan bahwa kapasitor bypass perlu melewati dua lubang ketika menghubungkan lapisan daya dan pembentukan, sehingga induktansi parasit lubang akan dikalikan.

Bagaimana cara menggunakan via?

Melalui analisis di atas dari karakteristik parasit dari lubang, kita dapat melihat bahwa dalam desain PCB berkecepatan tinggi, lubang yang tampaknya sederhana sering kali membawa efek negatif yang besar pada desain sirkuit. Untuk mengurangi efek samping yang disebabkan oleh efek parasit dari lubang, desain bisa sejauh mungkin:

Dari dua aspek biaya dan kualitas sinyal, pilih ukuran ukuran melalui yang wajar. Jika perlu, Anda dapat mempertimbangkan untuk menggunakan berbagai ukuran VIAS, seperti untuk catu daya atau lubang kawat ground, Anda dapat mempertimbangkan menggunakan ukuran yang lebih besar untuk mengurangi impedansi, dan untuk kabel sinyal, Anda dapat menggunakan via yang lebih kecil. Tentu saja, seukuran pengurangan via, biaya yang sesuai juga akan meningkat

Dua rumus yang dibahas di atas dapat disimpulkan bahwa penggunaan papan PCB yang lebih tipis kondusif untuk mengurangi dua parameter parasit via

Pengkabelan sinyal pada papan PCB tidak boleh diubah sejauh mungkin, yaitu, cobalah untuk tidak menggunakan vias yang tidak perlu.

Vias harus dibor ke dalam pin catu daya dan tanah. Semakin pendek keunggulan antara pin dan vias, semakin baik. Beberapa lubang dapat dibor secara paralel untuk mengurangi induktansi yang setara.

Tempatkan beberapa lubang yang membumi di dekat lubang-lubang dari perubahan sinyal untuk memberikan loop terdekat untuk sinyal. Anda bahkan dapat menempatkan beberapa lubang tanah berlebih di papan PCB.

Untuk papan PCB berkecepatan tinggi dengan kepadatan tinggi, Anda dapat mempertimbangkan menggunakan lubang mikro.