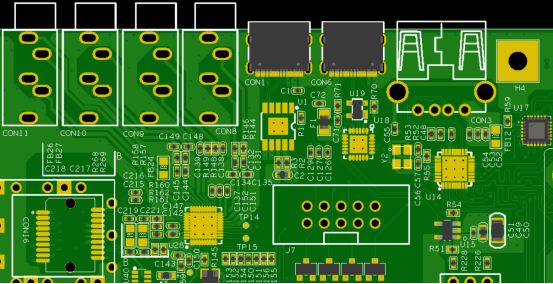

Konsènan Layout nan PCB ak pwoblèm fil elektrik, jodi a nou pa pral pale sou analiz entegrite siyal (SI), analiz konpatibilite elektwomayetik (EMC), analiz entegrite pouvwa (PI). Jis pale sou analiz la manufacturability (DFM), konsepsyon an rezonab nan manufacturability pral tou mennen nan echèk la nan konsepsyon pwodwi.

DFM ki gen siksè nan yon layout PCB kòmanse ak règleman konsepsyon anviwònman nan kont pou enpòtan kontrent DFM. Règ yo DFM yo montre anba a reflete kèk nan kapasite yo konsepsyon kontanporen ki pi manifaktirè ka jwenn. Asire ke limit yo mete nan règleman yo konsepsyon PCB pa vyole yo pou ke pi fò restriksyon konsepsyon estanda ka asire.

Pwoblèm nan DFM nan PCB routage depann sou yon Layout PCB bon, ak règleman yo routage ka prereglaj, ki gen ladan kantite fwa koube nan liy lan, ki kantite twou kondiksyon, ki kantite etap, elatriye. Anjeneral, se fil elektrik eksploratwa te pote soti premye konekte kout liy byen vit, ak Lè sa a, se labirent fil elektrik te pote soti. Se Global routage chemen optimize te pote soti sou fil yo yo dwe mete premye, ak re-fil elektrik yo te eseye amelyore efè a an jeneral ak DFM fabrike.

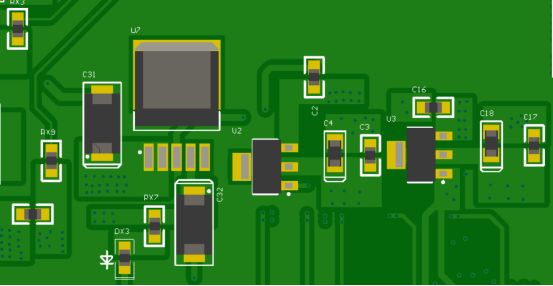

1.smt aparèy

Espas nan layout aparèy satisfè kondisyon yo asanble, epi li se jeneralman pi gran pase 20mil pou sifas monte aparèy, 80mil pou aparèy IC, ak 200mi pou aparèy BGA. Yo nan lòd yo amelyore bon jan kalite a ak sede nan pwosesis pwodiksyon an, espas la aparèy ka satisfè kondisyon yo asanble.

Anjeneral, distans ki genyen ant kousinen yo SMD nan broch yo aparèy yo ta dwe pi gran pase 6mil, ak kapasite nan fabwikasyon nan pon an soude soude se 4mil. Si distans ki genyen ant kousinen yo SMD se mwens pase 6mil ak distans ki genyen ant fenèt la soude se mwens pase 4mil, pon an soude pa ka kenbe, sa ki lakòz gwo moso nan soude (sitou ant broch yo) nan pwosesis la asanble, ki pral mennen nan kous kout.

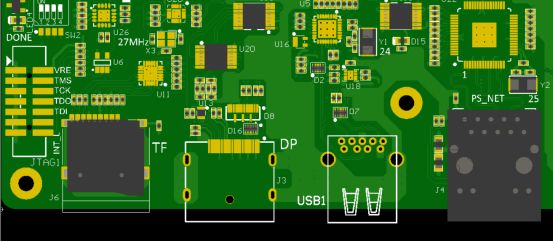

2.Dip aparèy

Espas PIN la, direksyon ak espas nan aparèy yo nan pwosesis la sou soudaj sou soudaj yo ta dwe pran an kont. Pa gen ase espas PIN nan aparèy la ap mennen nan soudaj fèblan, ki pral mennen nan kous kout.

Anpil konsèpteur minimize itilize nan nan-liy aparèy (THTs) oswa mete yo sou bò a menm nan tablo a. Sepandan, nan-liy aparèy yo souvan inevitab. Nan ka konbinezon, si yo mete aparèy nan liy lan sou kouch nan tèt ak aparèy la patch yo mete sou kouch anba a, nan kèk ka, li pral afekte yon sèl-bò vag soudaj la. Nan ka sa a, yo te itilize plis pwosesis soude, tankou soude selektif, yo te itilize.

3. Distans ki genyen ant eleman yo ak kwen plak la

Si li se soude machin, distans ki genyen ant eleman yo elektwonik ak kwen nan tablo a se jeneralman 7mm (diferan manifaktirè soude gen kondisyon diferan), men li kapab tou gen pou ajoute nan kwen nan pwosesis pwodiksyon PCB, se konsa ke eleman yo elektwonik ka mete sou kwen nan tablo PCB, osi lontan ke li se pratik pou fil elektrik.

Sepandan, lè se kwen nan plak la soude, li ka rankontre tren an gid nan machin nan ak domaje konpozan yo. Ap pad aparèy la nan kwen nan plak la dwe retire nan pwosesis la manifakti. Si pad la se ti, yo pral bon jan kalite a soude ap afekte.

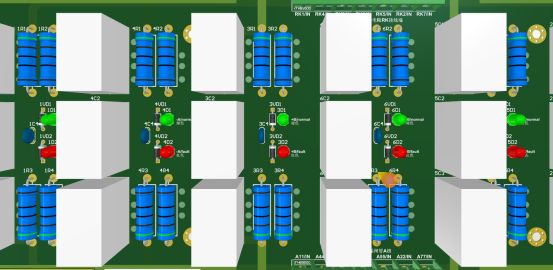

4.Distance nan aparèy segondè/ki ba

Gen anpil kalite konpozan elektwonik, diferan fòm, ak yon varyete de liy plon, se konsa gen diferans ki genyen nan metòd la asanble nan ankadreman enprime. Bon Layout pa ka sèlman fè machin nan pèfòmans ki estab, prèv chòk, diminye domaj, men tou, ka jwenn yon efè pwòp ak bèl andedan machin nan.

Ti aparèy yo dwe kenbe nan yon distans sèten alantou aparèy segondè. Distans aparèy la nan rapò a wotè aparèy se ti, gen yon vag tèmik inegal, ki ka lakòz risk pou yo soude pòv oswa reparasyon apre soude.

5.Device nan espas aparèy

An jeneral pwosesis SMT, li nesesè pran an kont sèten erè nan aliye nan machin nan, epi pran an kont konvenyans nan antretyen ak enspeksyon vizyèl. De eleman yo adjasan pa ta dwe twò pre ak yon sèten distans ki an sekirite yo ta dwe kite.

Espas ki genyen ant konpozan flokon, SOT, SOIC ak konpozan flok se 1.25mm. Espas ki genyen ant konpozan flokon, SOT, SOIC ak konpozan flok se 1.25mm. 2.5mm ant PLCC ak konpozan flokon, SOIC ak QFP. 4mm ant PLCCs. Lè konsepsyon sipò PLCC, swen yo ta dwe pran pou pèmèt pou gwosè a nan priz la PLCC (PIN la PLCC se andedan anba a nan priz la).

6. Distans lajè/liy

Pou konsèpteur, nan pwosesis la nan konsepsyon, nou ka pa sèlman konsidere presizyon an ak pèfeksyon nan kondisyon yo ki konsepsyon, gen yon restriksyon gwo se pwosesis pwodiksyon an. Li enposib pou yon faktori tablo yo kreye yon liy pwodiksyon nouvo pou nesans la nan yon bon pwodwi.

Anba kondisyon nòmal, se lajè liy lan nan liy lan desann kontwole a 4/4mil, epi li se twou a chwazi yo dwe 8mil (0.2mm). Fondamantalman, plis pase 80% nan manifaktirè PCB ka pwodwi, ak pri a pwodiksyon se pi ba la. Ka lajè a minimòm lajè ak distans liy dwe kontwole a 3/3mil, ak 6mil (0.15mm) ka chwazi nan twou a. Fondamantalman, plis pase 70% manifaktirè PCB ka pwodwi li, men pri a se yon ti kras pi wo pase ka a an premye, pa twòp pi wo.

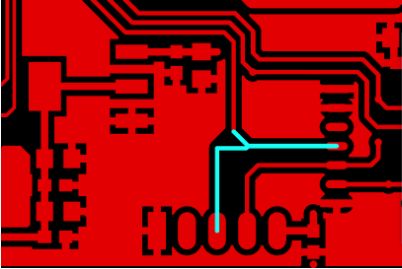

7. Yon ang egi/ang dwat

Se byen file routage ang jeneralman entèdi nan fil elektrik la, se routage ang dwat jeneralman oblije pou fè pou evite sitiyasyon an nan routage PCB, e li te prèske vin youn nan estanda yo ki mezire bon jan kalite a nan fil elektrik. Paske entegrite siyal la afekte, fil elektrik la ap jenere plis kapasite parazit ak enduktans.

Nan pwosesis la nan PCB plak-fè, fil PCB kwaze nan yon ang egi, ki pral lakòz yon pwoblèm yo rele ang asid. Nan sikwi a PCB Lyen grave, twòp korozyon nan sikwi PCB yo pral ki te koze nan "ang asid la", sa ki lakòz PCB sikwi a vityèl kraze pwoblèm. Se poutèt sa, enjenyè PCB bezwen pou fè pou evite ang byen file oswa etranj nan fil elektrik la, epi kenbe yon ang 45 degre nan kwen an nan fil elektrik la.

8. Copper Strip/Island

Si li se yon gwo kwiv ase zile, li pral vin yon antèn, ki ka lakòz bri ak lòt entèferans andedan tablo a (paske kòb kwiv mete li yo pa chita - li pral vin yon pèseptè siyal).

Bann kwiv ak zile yo se anpil kouch plat nan kwiv gratis-k ap flote, ki ka lakòz kèk pwoblèm grav nan depresyon an asid. Ti tach kwiv yo te konnen yo kraze nan panèl la PCB ak vwayaje nan lòt zòn grave sou panèl la, sa ki lakòz yon sikwi kout.

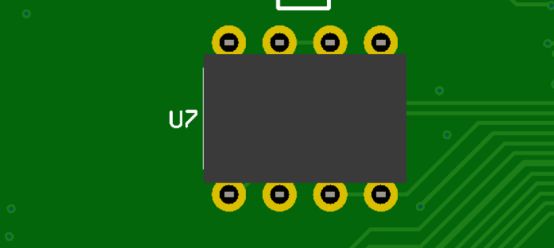

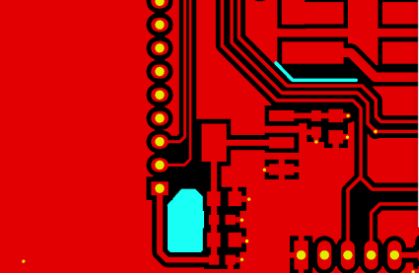

9. Ring nan twou perçage

Bag la twou refere a yon bag nan kwiv alantou twou a fè egzèsis. Akòz tolerans nan pwosesis manifakti a, apre yo fin perçage, grave, ak plato kwiv, bag an kwiv ki rete alantou twou a egzèsis pa toujou frape pwen nan sant nan pad la parfe, ki ka lakòz bag la twou kraze.

Yon bò nan bag la twou yo dwe pi gran pase 3.5mil, ak bag la ploge nan twou yo dwe pi gran pase 6mil. Bag la twou se twò piti. Nan pwosesis pwodiksyon ak manifakti, twou a perçage gen tolerans ak aliyman nan liy lan tou gen tolerans. Devyasyon nan tolerans la ap mennen nan bag la twou kraze kous la louvri.

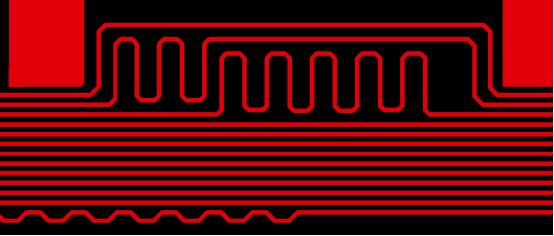

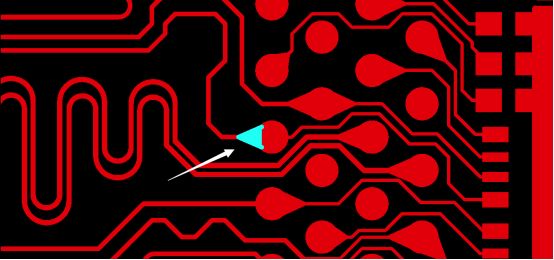

10. Dlo a dlo nan fil elektrik

Ajoute dlo nan je nan fil elektrik PCB ka fè koneksyon an sikwi sou tablo a PCB pi estab, segondè fyab, se konsa ke sistèm lan pral pi estab, kidonk li nesesè yo ajoute dlo nan je nan tablo a sikwi.

Adisyon a nan gout dlo ka evite dekoneksyon an nan pwen an kontak ant fil la ak pad la oswa fil la ak twou a pilòt lè se tablo a sikwi afekte pa yon gwo fòs ekstèn. Lè w ajoute gout dlo nan soude, li ka pwoteje pad a, evite soude miltip fè pad an tonbe, epi evite inegal grave ak fant ki te koze pa deformation twou pandan pwodiksyon an.