Entwodiksyon deVia-in-pad:

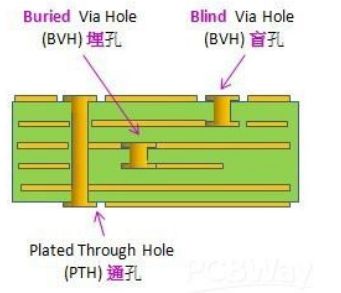

Li se byen li te ye ki VIAs (via) ka divize an plake nan twou, twou VIAs avèg ak antere l 'twou VIAS, ki gen fonksyon diferan.

Avèk devlopman nan pwodwi elektwonik, VIAs jwe yon wòl enpòtan anpil nan entèrkoneksyon an entèraksyon nan tablo sikwi enprime. Via-in-pad se lajman ki itilize nan ti PCB ak BGA (boul gri etalaj). Avèk devlopman inevitab nan dansite segondè, BGA (etalaj griy boul) ak SMD miniaturizasyon chip, aplikasyon an nan via-nan-pad teknoloji ap vin pi plis ak plis enpòtan.

Vias nan kousinen gen anpil avantaj sou avèg ak antere l ': VIAs:

. Apwopriye pou bon goud BGA.

. Li se pratik nan konsepsyon pi wo dansite PCB ak sove espas fil elektrik.

. Pi bon jesyon tèmik.

. Anti-ba enduktans ak lòt konsepsyon gwo vitès.

. Ofri yon sifas ki pi plat pou konpozan.

. Diminye zòn PCB ak plis amelyore fil elektrik.

Akòz avantaj sa yo, via-an-pad se lajman ki itilize nan PCBs ti, espesyalman nan desen PCB kote transfè chalè ak gwo vitès yo gen obligasyon ak anplasman BGA limite. Malgre ke VIAs avèg ak antere l 'ede ogmante dansite ak ekonomize espas sou PCB, VIAs nan kousinen yo toujou pi bon chwa a pou jesyon tèmik ak konpozan konsepsyon gwo vitès.

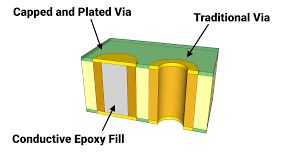

Avèk yon serye via ranpli/plating pwosesis limit, via-an-pad teknoloji ka itilize yo pwodwi segondè-dansite PCBs san yo pa itilize kay chimik ak evite soudaj erè. Anplis de sa, sa a ka bay plis fil konekte pou desen BGA.

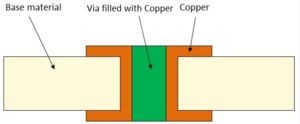

Gen divès kalite materyèl ranpli pou twou a nan plak la, keratin ajan ak keratin kwiv yo souvan itilize pou materyèl kondiktè, ak résine se souvan itilize pou materyèl ki pa kondiktif