વાયા એ મલ્ટી-લેયર પીસીબીના મહત્વના ઘટકોમાંનું એક છે, અને ડ્રિલિંગનો ખર્ચ સામાન્ય રીતે PCB બોર્ડના ખર્ચના 30% થી 40% જેટલો હોય છે. સરળ શબ્દોમાં કહીએ તો, PCB પરના દરેક છિદ્રને વાયા કહી શકાય.

દ્વારા મૂળભૂત ખ્યાલ:

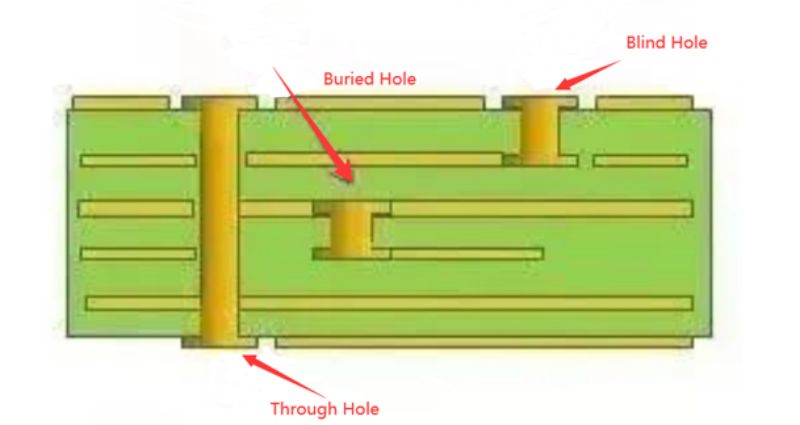

કાર્યના દૃષ્ટિકોણથી, વાયાને બે કેટેગરીમાં વિભાજિત કરી શકાય છે: એકનો ઉપયોગ સ્તરો વચ્ચેના વિદ્યુત જોડાણ તરીકે થાય છે, અને બીજાનો ઉપયોગ ઉપકરણના ફિક્સિંગ અથવા સ્થિતિ તરીકે થાય છે. જો પ્રક્રિયામાંથી, આ છિદ્રોને સામાન્ય રીતે ત્રણ શ્રેણીઓમાં વિભાજિત કરવામાં આવે છે, એટલે કે અંધ છિદ્રો, દફનાવવામાં આવેલા છિદ્રો અને છિદ્રો દ્વારા.

અંધ છિદ્રો પ્રિન્ટેડ સર્કિટ બોર્ડની ઉપર અને નીચેની સપાટી પર સ્થિત હોય છે અને સપાટીના સર્કિટ અને નીચેના આંતરિક સર્કિટના જોડાણ માટે ચોક્કસ ઊંડાઈ ધરાવે છે, અને છિદ્રોની ઊંડાઈ સામાન્ય રીતે ચોક્કસ ગુણોત્તર (બાકોરું) કરતાં વધી જતી નથી.

દફનાવવામાં આવેલ છિદ્ર પ્રિન્ટેડ સર્કિટ બોર્ડના આંતરિક સ્તરમાં સ્થિત કનેક્શન છિદ્રનો સંદર્ભ આપે છે, જે બોર્ડની સપાટી સુધી વિસ્તરતું નથી. ઉપરોક્ત બે પ્રકારના છિદ્રો સર્કિટ બોર્ડના આંતરિક સ્તરમાં સ્થિત છે, જે લેમિનેશન પહેલાં થ્રુ હોલ મોલ્ડિંગ પ્રક્રિયા દ્વારા પૂર્ણ થાય છે, અને થ્રુ હોલની રચના દરમિયાન કેટલાક આંતરિક સ્તરો ઓવરલેપ થઈ શકે છે.

ત્રીજા પ્રકારને થ્રુ-હોલ્સ કહેવામાં આવે છે, જે સમગ્ર સર્કિટ બોર્ડમાંથી પસાર થાય છે અને તેનો ઉપયોગ આંતરિક ઇન્ટરકનેક્શન હાંસલ કરવા અથવા ઘટકો માટે ઇન્સ્ટોલેશન પોઝિશનિંગ છિદ્રો તરીકે થઈ શકે છે. કારણ કે પ્રક્રિયામાં થ્રુ હોલ પ્રાપ્ત કરવું સરળ છે અને તેની કિંમત ઓછી છે, મોટા ભાગના પ્રિન્ટેડ સર્કિટ બોર્ડ તેનો ઉપયોગ કરે છે, અન્ય બે છિદ્રોને બદલે. નીચેના છિદ્રો, ખાસ સૂચનાઓ વિના, છિદ્રો દ્વારા ગણવામાં આવે છે.

ડિઝાઇનના દૃષ્ટિકોણથી, વાયા મુખ્યત્વે બે ભાગોથી બનેલું છે, એક ડ્રિલિંગ છિદ્રની મધ્યમાં છે, અને બીજો ડ્રિલિંગ છિદ્રની આસપાસ વેલ્ડિંગ પેડ વિસ્તાર છે. આ બે ભાગોનું કદ વાયાનું કદ નક્કી કરે છે.

દેખીતી રીતે, હાઇ-સ્પીડ, હાઇ-ડેન્સિટી પીસીબી ડિઝાઇનમાં, ડિઝાઇનર્સ હંમેશા શક્ય તેટલું નાનું છિદ્ર ઇચ્છે છે, જેથી વધુ વાયરિંગ જગ્યા છોડી શકાય, વધુમાં, વાયા જેટલી નાની, તેની પોતાની પરોપજીવી કેપેસીટન્સ નાની, વધુ યોગ્ય હોય છે. હાઇ-સ્પીડ સર્કિટ માટે.

જો કે, વાયાના કદના ઘટાડાથી ખર્ચમાં પણ વધારો થાય છે, અને છિદ્રનું કદ અનિશ્ચિત સમય માટે ઘટાડી શકાતું નથી, તે ડ્રિલિંગ અને ઇલેક્ટ્રોપ્લેટિંગ તકનીક દ્વારા મર્યાદિત છે: છિદ્ર જેટલું નાનું છે, ડ્રિલિંગ જેટલું લાંબું લે છે, તેટલું સરળ કેન્દ્રમાંથી વિચલિત થવું છે; જ્યારે છિદ્રની ઊંડાઈ છિદ્રના વ્યાસ કરતાં 6 ગણા કરતાં વધુ હોય છે, ત્યારે તે ખાતરી કરવી અશક્ય છે કે છિદ્રની દિવાલ એકસરખી રીતે તાંબાથી પ્લેટેડ થઈ શકે છે.

ઉદાહરણ તરીકે, જો સામાન્ય 6-સ્તર PCB બોર્ડની જાડાઈ (છિદ્રની ઊંડાઈ દ્વારા) 50Mil હોય, તો PCB ઉત્પાદકો સામાન્ય સ્થિતિમાં પ્રદાન કરી શકે તે ન્યૂનતમ ડ્રિલિંગ વ્યાસ માત્ર 8Mil સુધી પહોંચી શકે છે. લેસર ડ્રિલિંગ ટેક્નોલોજીના વિકાસ સાથે, ડ્રિલિંગનું કદ પણ નાનું અને નાનું હોઈ શકે છે, અને છિદ્રનો વ્યાસ સામાન્ય રીતે 6Mils કરતા ઓછો અથવા બરાબર હોય છે, અમને માઇક્રોહોલ કહેવામાં આવે છે.

માઇક્રોહોલનો ઉપયોગ ઘણીવાર HDI (ઉચ્ચ ઘનતા ઇન્ટરકનેક્ટ સ્ટ્રક્ચર) ડિઝાઇનમાં થાય છે, અને માઇક્રોહોલ ટેક્નોલોજી પેડ પર સીધા છિદ્રને ડ્રિલ કરવાની મંજૂરી આપી શકે છે, જે સર્કિટની કામગીરીમાં ઘણો સુધારો કરે છે અને વાયરિંગની જગ્યા બચાવે છે. વાયા ટ્રાન્સમિશન લાઇન પર અવબાધ બંધ થવાના બ્રેકપોઇન્ટ તરીકે દેખાય છે, જેના કારણે સિગ્નલનું પ્રતિબિંબ પડે છે. સામાન્ય રીતે, છિદ્રની સમકક્ષ અવબાધ ટ્રાન્સમિશન લાઇન કરતાં લગભગ 12% નીચી હોય છે, ઉદાહરણ તરીકે, 50 ઓહ્મ ટ્રાન્સમિશન લાઇનની અવબાધ જ્યારે છિદ્રમાંથી પસાર થાય છે ત્યારે તે 6 ઓહ્મથી ઘટશે (ખાસ કરીને અને વાયાનું કદ, પ્લેટની જાડાઈ પણ સંબંધિત છે, સંપૂર્ણ ઘટાડો નહીં).

જો કે, વાસ્તવમાં અવબાધની અસંતુલિતતાને કારણે થતું પ્રતિબિંબ ખૂબ જ નાનું છે, અને તેનું પ્રતિબિંબ ગુણાંક માત્ર છે:

(44-50)/(44 + 50) = 0.06

વાયાથી ઉદ્ભવતી સમસ્યાઓ પરોપજીવી કેપેસીટન્સ અને ઇન્ડક્ટન્સની અસરો પર વધુ કેન્દ્રિત છે.

વાયાની પરોપજીવી કેપેસિટીન્સ અને ઇન્ડક્ટન્સ

વાયામાં જ પરોપજીવી સ્ટ્રે કેપેસીટીન્સ છે. જો નાખેલા સ્તર પર સોલ્ડર રેઝિસ્ટન્સ ઝોનનો વ્યાસ D2 છે, સોલ્ડર પેડનો વ્યાસ D1 છે, PCB બોર્ડની જાડાઈ T છે, અને સબસ્ટ્રેટનો ડાઇલેક્ટ્રિક કોન્સ્ટન્ટ ε છે, થ્રુ હોલની પરોપજીવી કેપેસિટીન્સ આશરે છે:

C=1.41εTD1/(D2-D1)

સર્કિટ પર પરોપજીવી કેપેસીટન્સની મુખ્ય અસર સિગ્નલના ઉદય સમયને લંબાવવી અને સર્કિટની ઝડપને ઘટાડવાની છે.

ઉદાહરણ તરીકે, 50Mil ની જાડાઈ ધરાવતા PCB માટે, જો વાયા પેડનો વ્યાસ 20Mil છે (ડ્રિલિંગ છિદ્રનો વ્યાસ 10Mil છે) અને સોલ્ડર રેઝિસ્ટન્સ ઝોનનો વ્યાસ 40Mil છે, તો આપણે પરોપજીવી કેપેસીટન્સનો અંદાજ લગાવી શકીએ છીએ. ઉપરોક્ત સૂત્ર દ્વારા:

C=1.41x4.4x0.050x0.020/(0.040-0.020)=0.31pF

કેપેસિટેન્સના આ ભાગને કારણે ઉદય સમયના ફેરફારની માત્રા આશરે છે:

T10-90=2.2C(Z0/2)=2.2x0.31x(50/2)=17.05ps

આ મૂલ્યો પરથી જોઈ શકાય છે કે સિંગલ વાયાના પરોપજીવી કેપેસિટેન્સને કારણે થતા ઉદય વિલંબની ઉપયોગિતા બહુ સ્પષ્ટ નથી, જો સ્તરો વચ્ચે સ્વિચ કરવા માટે લાઇનમાં ઘણી વખત વાયાનો ઉપયોગ કરવામાં આવે, તો બહુવિધ છિદ્રોનો ઉપયોગ કરવામાં આવશે, અને ડિઝાઇન કાળજીપૂર્વક ધ્યાનમાં લેવી જોઈએ. વાસ્તવિક ડિઝાઇનમાં, છિદ્ર અને તાંબાના વિસ્તાર (એન્ટી-પેડ) વચ્ચેનું અંતર વધારીને અથવા પેડનો વ્યાસ ઘટાડીને પરોપજીવી કેપેસીટન્સ ઘટાડી શકાય છે.

હાઇ-સ્પીડ ડિજિટલ સર્કિટ્સની ડિઝાઇનમાં, પરોપજીવી ઇન્ડક્ટન્સને કારણે થતું નુકસાન ઘણીવાર પરોપજીવી કેપેસીટન્સના પ્રભાવ કરતાં વધારે હોય છે. તેની પરોપજીવી શ્રેણીના ઇન્ડક્ટન્સ બાયપાસ કેપેસિટરના યોગદાનને નબળું પાડશે અને સમગ્ર પાવર સિસ્ટમની ફિલ્ટરિંગ અસરકારકતાને નબળી પાડશે.

થ્રુ-હોલ એપ્રોક્સિમેશનના પરોપજીવી ઇન્ડક્ટન્સની ગણતરી કરવા માટે અમે નીચેના પ્રયોગમૂલક સૂત્રનો ઉપયોગ કરી શકીએ છીએ:

L=5.08h[ln(4h/d)+1]

જ્યાં L એ વાયાના ઇન્ડક્ટન્સનો ઉલ્લેખ કરે છે, h એ વાયાની લંબાઈ છે અને d એ કેન્દ્રિય છિદ્રનો વ્યાસ છે. તે સૂત્ર પરથી જોઈ શકાય છે કે વાયાનો વ્યાસ ઇન્ડક્ટન્સ પર ઓછો પ્રભાવ ધરાવે છે, જ્યારે વાયાની લંબાઈ ઇન્ડક્ટન્સ પર સૌથી વધુ પ્રભાવ ધરાવે છે. હજુ પણ ઉપરોક્ત ઉદાહરણનો ઉપયોગ કરીને, આઉટ-ઓફ-હોલ ઇન્ડક્ટન્સની ગણતરી આ રીતે કરી શકાય છે:

L=5.08x0.050[ln(4x0.050/0.010)+1]=1.015nH

જો સિગ્નલનો ઉદય સમય 1ns છે, તો તેની સમકક્ષ અવબાધ કદ છે:

XL=πL/T10-90=3.19Ω

આવા અવબાધને ઉચ્ચ-આવર્તન પ્રવાહની હાજરીમાં અવગણી શકાય નહીં, ખાસ કરીને, નોંધ કરો કે બાયપાસ કેપેસિટરને પાવર લેયર અને રચનાને જોડતી વખતે બે છિદ્રોમાંથી પસાર થવાની જરૂર છે, જેથી છિદ્રના પરોપજીવી ઇન્ડક્ટન્સનો ગુણાકાર થશે.

વાયાનો ઉપયોગ કેવી રીતે કરવો?

છિદ્રની પરોપજીવી લાક્ષણિકતાઓના ઉપરોક્ત વિશ્લેષણ દ્વારા, આપણે જોઈ શકીએ છીએ કે હાઇ-સ્પીડ PCB ડિઝાઇનમાં, મોટે ભાગે સરળ દેખાતા છિદ્રો સર્કિટની ડિઝાઇનમાં ઘણી નકારાત્મક અસરો લાવે છે. છિદ્રની પરોપજીવી અસરને કારણે થતી પ્રતિકૂળ અસરોને ઘટાડવા માટે, ડિઝાઇન શક્ય હોય ત્યાં સુધી હોઈ શકે છે:

કિંમત અને સિગ્નલ ગુણવત્તાના બે પાસાઓમાંથી, વાયા કદનું વાજબી કદ પસંદ કરો. જો જરૂરી હોય તો, તમે વીજ પુરવઠો અથવા ગ્રાઉન્ડ વાયર છિદ્રો જેવા વિવિધ કદના વાયરનો ઉપયોગ કરવાનું વિચારી શકો છો, તમે અવરોધ ઘટાડવા માટે મોટા કદનો ઉપયોગ કરવાનું વિચારી શકો છો, અને સિગ્નલ વાયરિંગ માટે, તમે નાના વાયાનો ઉપયોગ કરી શકો છો. અલબત્ત, જેમ જેમ વાયાનું કદ ઘટશે તેમ તેમ અનુરૂપ ખર્ચ પણ વધશે

ઉપરોક્ત ચર્ચા કરાયેલા બે સૂત્રો પરથી નિષ્કર્ષ પર આવી શકાય છે કે પાતળા PCB બોર્ડનો ઉપયોગ બે પરોપજીવી પરિમાણોને ઘટાડવા માટે અનુકૂળ છે.

PCB બોર્ડ પરના સિગ્નલ વાયરિંગને શક્ય હોય ત્યાં સુધી બદલવું જોઈએ નહીં, એટલે કે બિનજરૂરી વાયાનો ઉપયોગ ન કરવાનો પ્રયાસ કરો.

વીઆસને પાવર સપ્લાયના પિન અને જમીનમાં ડ્રિલ કરવું આવશ્યક છે. પિન અને વિઆસ વચ્ચેની લીડ જેટલી ટૂંકી હશે તેટલું સારું. સમકક્ષ ઇન્ડક્ટન્સ ઘટાડવા માટે સમાંતરમાં બહુવિધ છિદ્રો ડ્રિલ કરી શકાય છે.

સિગ્નલ માટે સૌથી નજીકનો લૂપ પૂરો પાડવા માટે સિગ્નલ ચેન્જના થ્રુ-હોલ્સની નજીક કેટલાક ગ્રાઉન્ડેડ થ્રુ-હોલ્સ મૂકો. તમે PCB બોર્ડ પર કેટલાક વધારાના ગ્રાઉન્ડ હોલ પણ મૂકી શકો છો.

ઉચ્ચ ઘનતાવાળા હાઇ સ્પીડ પીસીબી બોર્ડ માટે, તમે માઇક્રો-હોલ્સનો ઉપયોગ કરવાનું વિચારી શકો છો.