Wannear meitsje dePCB-routing, Fanwegen it progress fan it foarriedige analyse is net dien of net dien, is de postferwurking lestich. As it PCB-bestjoer wurdt fergelike mei ús stêd, binne de komponinten op rige fan alle soarten gebouwen, binne signale-strepen en gnysken, Flyover RoundaVant RoundaN Round de detaillearre planning, wiring is ek itselde.

1 easken foar prioriteit fan draadprioriteit

A) Key-sinjaallinen binne de foarkar: Power-oanbod, analoge lyts sinjaal, hege sinjaal, Clock Signal, Signatedsignal en oare wichtige sinjalen wurde de foarkar.

B) WIRING TENSITY PRIORITY PRIORITY PRIORITY PRIORITY: Begjin wiring út 'e komponint mei de meast komplekse ferbiningferhâlding op it boerd. Cabling begjint fan it meast ticht ferbûn gebiet op it boerd.

C) foarsoarchsmaatregels foar ferwurkjen fan wichtige sinjaal: Besykje spesjale draadferfier te jaan foar wichtige sinjaal, lykas Clock-sinjaal, sinjaal en gefoelige sinjaal, en soargje foar it minimale loop-gebiet. As nedich, beskerming en ferheegje it ferheegjen fan it feiligenssplakken soe moatte wurde oannaam. Soargje foar sinjaalkwaliteit.

D) It netwurk fan it netwurkkontrôle-easken sil wurde regele op 'e lagen fan' e ympuls-kontrôle, en har sinjaal-divyzje wurdt foarkommen.

2.Wiring Scrambler Control

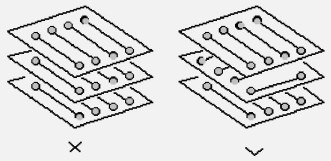

A) ynterpretaasje fan it 3W prinsipe

De ôfstân tusken de rigels moatte 3 kear de line breedte wêze. Om krystend tusken rigels te ferminderjen, soe de line-spaasjes grut genôch wêze moatte. As de ôfstânôfstân net minder is as 3 kear de line breedte, 70% fan it elektryske fjild tusken rigels kinne wurde bewarre sûnder ynterferinsje, dy't de 3W-regel hjit.

B) Tampering Control: CrosStalk ferwiist nei de ûnderlinge ynterferinsje tusken ferskate netwurken op PCB feroarsake troch lange parallel-draad, fral troch de aksje fan ferdield en ferspraat yndutens tusken parallelle rigels. De wichtichste maatregels om krystlik te oerwinnen binne:

I. Fergrutsje it spaasje fan parallelle kabels en folgje de 3w regel;

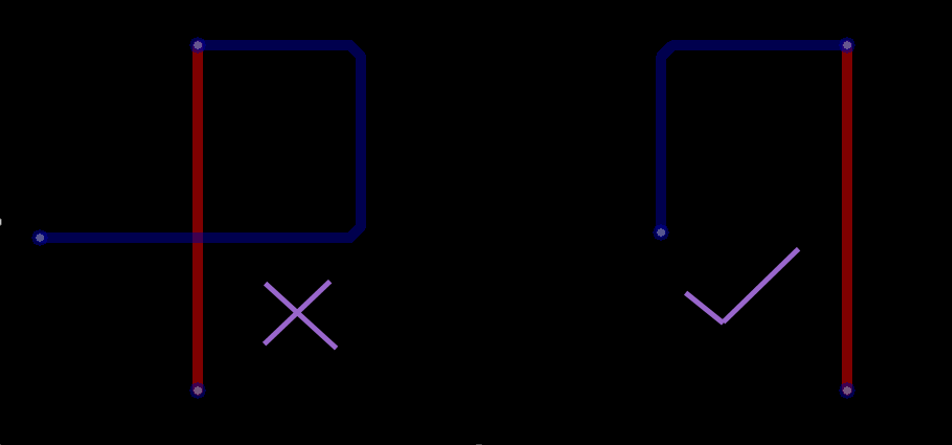

II. Ynfoegje kabels foar grûn isolaasje tusken parallelle kabels

III. Ferminderje de ôfstân tusken de kablinglaach en it grûnplan.

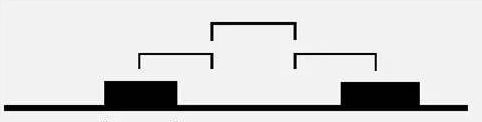

3. Algemiene regels foar it draaiende easken

A) de rjochting fan it oanswettende fleantúch is orthogonaal. Foarkom de ferskillende sinjaal rigels yn 'e oanswettende laach yn deselde rjochting om ûnnedige ynter-laach tamper te ferminderjen; As dizze situaasje lestich is om te foarkommen fanwegen beheiningen fan boerdstruktuer),, foaral as it sinjaal heech is, moatte jo wat plekers beskôgje op it grûnfleantúch en sinjale kabels op 'e grûn.

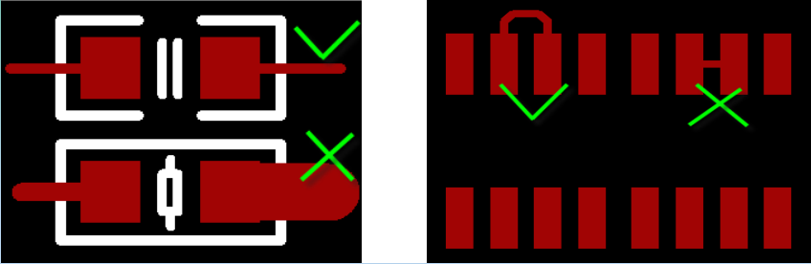

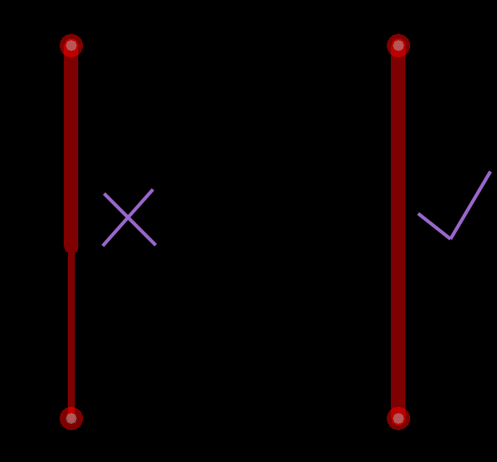

B) It draad fan lytse diskrete-apparaten moatte symmetrysk wêze, en it SMT-pad leads mei relatyf slútspaasje moatte ferbûn wêze fan 'e bûtenkant fan it pad. Direkte ferbining yn 'e midden fan' e pad is net tastien.

C) Minimale loopregel, dat is, it gebiet fan 'e loop foarme troch de sinjaal-line en syn loop soe sa lyts mooglik wêze moatte. De lytsere it gebiet fan 'e loop, hoe minder de eksterne strieling en de lytsere de eksterne ynterferinsje.

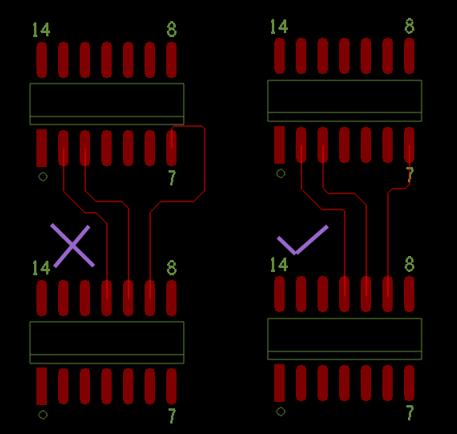

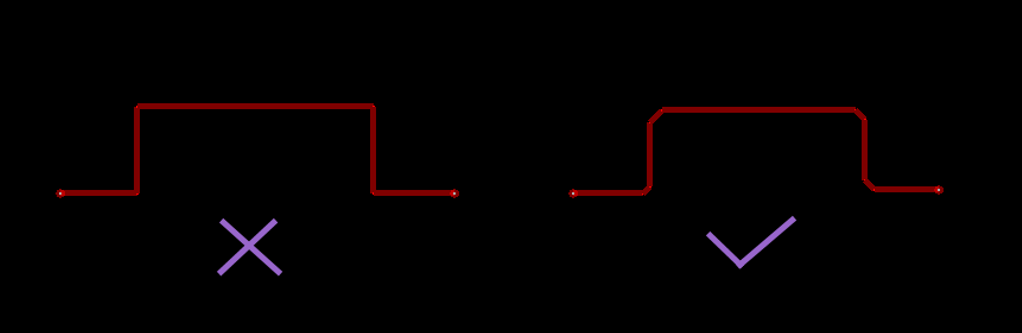

D) kabels kabels binne net tastien

E) De wiringbreedte fan itselde netwurk moat itselde wurde hâlden. De fariaasje fan 'e draadbreedte sil de uneven karakteristike ympuls fan' e line feroarsaakje. As de oerdrachtnelheid heech is, sil refleksje foarkomme. Under guon omstannichheden, lykas de ferbiningsload-liedich wire, lieden fan BGA-pakket, om't de lytse spaasje miskien de feroaring fan 'e linebreedte net kin foarkomme, moatte besykje de effektive lingte fan it middenynkonsekwint diel te ferminderjen.

F) foarkomme dat sinjalen dy't sels-loops foarmje tusken ferskate lagen. Dit soarte fan probleem is maklik om te foarkommen yn it ûntwerp fan meardere platen, en de sels-loop sil strieling ynterferinsje feroarsaakje.

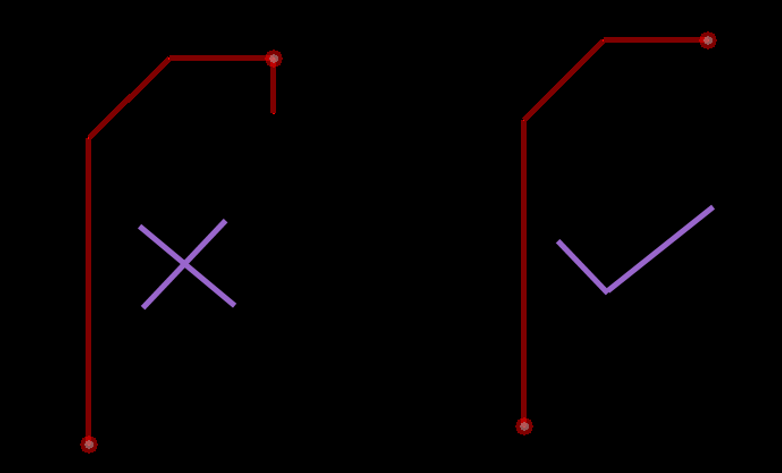

G) akute hoeke en rjochter hoeke moat yn foarkommen wurdePCB Untwerp, wat resulteart yn ûnnedige strieling, en de prestaasjes fan de produksjeproses fanPcbis net goed.