Mae'r VIA yn un o gydrannau pwysig PCB aml-haen, ac mae cost drilio fel arfer yn cyfrif am 30% i 40% o gost bwrdd PCB. Yn syml, gellir galw pob twll ar y PCB yn Via.

Cysyniad sylfaenol y VIA:

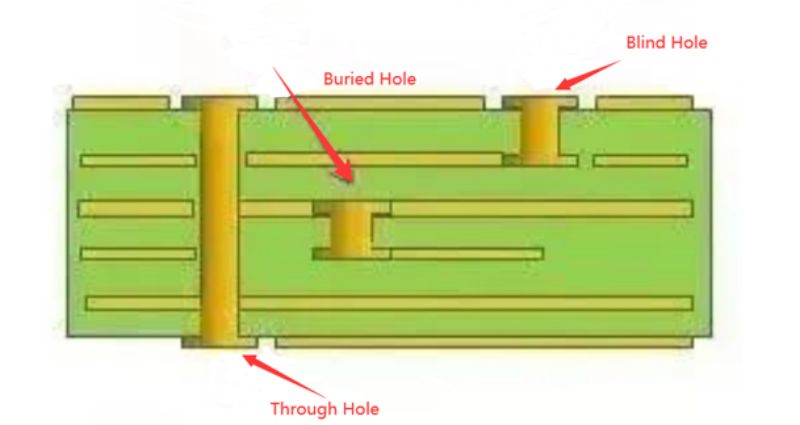

O safbwynt swyddogaeth, gellir rhannu'r Via yn ddau gategori: defnyddir un fel cysylltiad trydanol rhwng yr haenau, a defnyddir y llall fel trwsio neu leoli'r ddyfais. Os o'r broses, mae'r tyllau hyn yn gyffredinol wedi'u rhannu'n dri chategori, sef tyllau dall, tyllau wedi'u claddu a thrwy dyllau.

Mae tyllau dall wedi'u lleoli ar arwynebau uchaf a gwaelod y bwrdd cylched printiedig ac mae ganddynt ddyfnder penodol ar gyfer cysylltu'r gylched wyneb a'r gylched fewnol islaw, ac fel rheol nid yw dyfnder y tyllau yn fwy na chymhareb benodol (agorfa).

Mae'r twll claddedig yn cyfeirio at y twll cysylltu sydd wedi'i leoli yn haen fewnol y bwrdd cylched printiedig, nad yw'n ymestyn i wyneb y bwrdd. Mae'r ddau fath uchod o dwll wedi'u lleoli yn haen fewnol y bwrdd cylched, sy'n cael ei gwblhau gan y broses mowldio twll trwy lamineiddio, a gellir gorgyffwrdd sawl haen fewnol wrth ffurfio'r twll trwodd.

Gelwir y trydydd math yn dyllau trwy dyllau, sy'n mynd trwy'r bwrdd cylched cyfan a gellir ei ddefnyddio i gyflawni rhyng-gysylltiad mewnol neu fel tyllau lleoli gosod ar gyfer cydrannau. Oherwydd ei bod yn haws cyflawni'r twll trwy y broses ac mae'r gost yn is, mae mwyafrif helaeth y byrddau cylched printiedig yn ei ddefnyddio, yn hytrach na'r ddau arall trwy dyllau. Mae'r tyllau canlynol, heb gyfarwyddiadau arbennig, yn cael eu hystyried fel trwy dyllau.

O safbwynt dylunio, mae VIA yn cynnwys dwy ran yn bennaf, un yw canol y twll drilio, a'r llall yw'r ardal pad weldio o amgylch y twll drilio. Mae maint y ddwy ran hon yn pennu maint VIA.

Yn amlwg, mewn dyluniad PCB cyflymder uchel, dwysedd uchel, mae'r dylunwyr bob amser eisiau'r twll mor fach â phosib, fel y gellir gadael mwy o le gwifrau, yn ogystal, y lleiaf y Via, ei gynhwysedd parasitig ei hun yn llai, yn fwy addas ar gyfer cylchedau cyflym.

Fodd bynnag, mae lleihau'r maint VIA hefyd yn arwain at gynnydd mewn costau, ac ni ellir lleihau maint y twll am gyfnod amhenodol, mae'n gyfyngedig gan dechnoleg drilio ac electroplatio: po leiaf yw'r twll, yr hiraf y mae'r drilio yn ei gymryd, yr hawsaf yw gwyro o'r canol; Pan fydd dyfnder y twll fwy na 6 gwaith diamedr y twll, mae'n amhosibl sicrhau y gellir platio wal y twll yn unffurf â chopr.

Er enghraifft, os yw trwch (trwy ddyfnder twll) bwrdd PCB 6-haen arferol yn 50mil, yna dim ond 8mil y gall y diamedr drilio lleiaf y gall gweithgynhyrchwyr PCB ei ddarparu o dan amodau arferol gyrraedd 8mil. Gyda datblygiad technoleg drilio laser, gall maint y drilio hefyd fod yn llai ac yn llai, ac mae diamedr y twll yn gyffredinol yn llai na neu'n hafal i 6mils, fe'n gelwir yn ficro -doliau.

Defnyddir micro -tyllau yn aml mewn dyluniad HDI (strwythur rhyng -gysylltiad dwysedd uchel), a gall technoleg micro -dwll ganiatáu i'r twll gael ei ddrilio'n uniongyrchol ar y pad, sy'n gwella perfformiad y gylched yn fawr ac yn arbed y lle gwifrau. Mae'r Via yn ymddangos fel torbwynt o ddiffyg parhad rhwystriant ar y llinell drosglwyddo, gan achosi adlewyrchiad o'r signal. Yn gyffredinol, mae rhwystriant cyfatebol y twll tua 12% yn is na'r llinell drosglwyddo, er enghraifft, bydd rhwystriant llinell drosglwyddo 50 ohms yn cael ei leihau 6 ohms pan fydd yn mynd trwy'r twll (yn benodol a maint y tref, mae trwch y plât hefyd yn gysylltiedig, nid yn lleihad absoliwt).

Fodd bynnag, mae'r adlewyrchiad a achosir gan ddiffyg parhad y rhwystriant yn fach iawn mewn gwirionedd, ac yn unig yw ei gyfernod adlewyrchu:

(44-50)/(44 + 50) = 0.06

Mae'r problemau sy'n deillio o'r VA yn canolbwyntio mwy ar effeithiau cynhwysedd parasitig ac anwythiad.

Cynhwysedd ac anwythiad parasitig Via

Mae cynhwysedd crwydr parasitig yn y trwodd ei hun. Os mai diamedr y parth gwrthiant sodr ar yr haen gosod yw D2, diamedr y pad sodr yw D1, trwch y bwrdd PCB yw T, a chysonyn dielectrig y swbstrad yw ε, cynhwysedd parasitig y twll trwy drwodd yw: yn fras:

C = 1.41εtd1/(d2-d1)

Prif effaith y cynhwysedd parasitig ar y gylched yw estyn amser codi'r signal a lleihau cyflymder y gylched.

Er enghraifft, ar gyfer PCB â thrwch o 50 mmil, os yw diamedr y pad VIA yn 20 mmil (diamedr y twll drilio yw 10mils) a diamedr y parth gwrthiant sodr yw 40mil, yna gallwn amcangyfrif cynhwysedd parasitig y fformiwla uchod:

C = 1.41x4.4x0.050x0.020/(0.040-0.020) = 0.31pf

Mae maint y newid amser codi a achosir gan y rhan hon o'r cynhwysedd yn fras:

T10-90 = 2.2C (Z0/2) = 2.2x0.31x (50/2) = 17.05ps

Gellir gweld o'r gwerthoedd hyn, er nad yw defnyddioldeb yr oedi codi a achosir gan gynhwysedd parasitig un VIA yn amlwg iawn, os defnyddir y VIA sawl gwaith yn y llinell i newid rhwng haenau, bydd tyllau lluosog yn cael eu defnyddio, a dylid ystyried y dyluniad yn ofalus. Yn y dyluniad gwirioneddol, gellir lleihau'r cynhwysedd parasitig trwy gynyddu'r pellter rhwng y twll a'r ardal gopr (gwrth-bad) neu leihau diamedr y pad.

Wrth ddylunio cylchedau digidol cyflym, mae'r niwed a achosir gan yr anwythiad parasitig yn aml yn fwy na dylanwad y cynhwysedd parasitig. Bydd ei anwythiad cyfres barasitig yn gwanhau cyfraniad y cynhwysydd ffordd osgoi ac yn gwanhau effeithiolrwydd hidlo'r system bŵer gyfan.

Gallwn ddefnyddio'r fformiwla empirig ganlynol i gyfrifo anwythiad parasitig brasamcan twll trwodd:

L = 5.08h [ln (4h/d) +1]

Lle mae L yn cyfeirio at anwythiad Via, h yw hyd Via, a D yw diamedr y twll canolog. Gellir gweld o'r fformiwla nad oes gan ddiamedr y Via fawr o ddylanwad ar y inductance, tra bod hyd y VIA yn cael y dylanwad mwyaf ar yr anwythiad. Yn dal i ddefnyddio'r enghraifft uchod, gellir cyfrifo'r anwythiad y tu allan i'r twll fel:

L = 5.08x0.050 [ln (4x0.050/0.010) +1] = 1.015NH

Os yw amser codi'r signal yn 1Ns, yna ei faint rhwystriant cyfatebol yw:

Xl = πl/t10-90 = 3.19Ω

Ni ellir anwybyddu rhwystriant o'r fath ym mhresenoldeb cerrynt amledd uchel trwy, yn benodol, nodwch fod angen i'r cynhwysydd ffordd osgoi basio trwy ddau dwll wrth gysylltu'r haen bŵer a'r ffurfiant, fel y bydd anwythiad parasitig y twll yn cael ei luosi.

Sut i ddefnyddio'r Via?

Trwy'r dadansoddiad uchod o nodweddion parasitig y twll, gallwn weld, mewn dyluniad PCB cyflym, bod tyllau sy'n ymddangos yn syml yn aml yn dod ag effeithiau negyddol mawr i ddyluniad y gylched. Er mwyn lleihau'r effeithiau andwyol a achosir gan effaith barasitig y twll, gall y dyluniad fod cyn belled ag y bo modd:

O'r ddwy agwedd ar gost cost ac signal, dewiswch faint rhesymol o'r maint trwy faint. Os oes angen, gallwch ystyried defnyddio gwahanol feintiau o Vias, megis ar gyfer cyflenwad pŵer neu dyllau gwifren daear, gallwch ystyried defnyddio maint mwy i leihau'r rhwystriant, ac ar gyfer gwifrau signal, gallwch ddefnyddio trwyddo llai. Wrth gwrs, wrth i faint y VIA ostwng, bydd y gost gyfatebol hefyd yn cynyddu

Gellir dod i'r casgliad bod y ddau fformiwla a drafodwyd uchod

Ni ddylid newid y gwifrau signal ar y bwrdd PCB cyn belled ag y bo modd, hynny yw, ceisiwch beidio â defnyddio Vias diangen.

Rhaid drilio vias i binnau'r cyflenwad pŵer a'r ddaear. Po fyrraf yw'r plwm rhwng y pinnau a'r vias, y gorau. Gellir drilio tyllau lluosog yn gyfochrog i leihau'r anwythiad cyfatebol.

Rhowch ychydig o dyllau trwy dyllau ger tyllau trwodd y newid signal i ddarparu'r ddolen agosaf ar gyfer y signal. Gallwch hyd yn oed osod rhai tyllau tir gormodol ar y bwrdd PCB.

Ar gyfer byrddau PCB cyflym gyda dwysedd uchel, gallwch ystyried defnyddio micro-dyllau.