La VIA és un dels components importants del PCB de diverses capes i el cost de la perforació sol representar del 30% al 40% del cost de la placa de PCB. En poques paraules, cada forat del PCB es pot anomenar a via.

El concepte bàsic de la via:

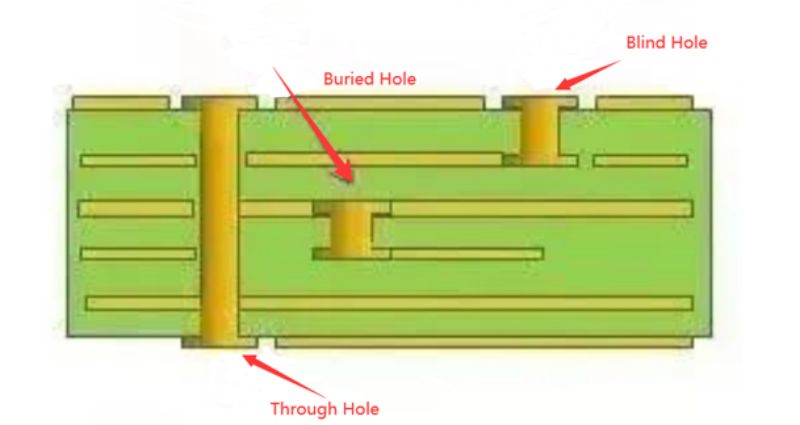

Des del punt de vista de la funció, la via es pot dividir en dues categories: una s’utilitza com a connexió elèctrica entre les capes i l’altra s’utilitza com a fixació o posicionament del dispositiu. Si del procés, aquests forats es divideixen generalment en tres categories, a saber, forats cecs, forats enterrats i a través de forats.

Els forats cecs es troben a la superfície superior i inferior de la placa de circuit imprès i tenen una certa profunditat per a la connexió del circuit superficial i el circuit interior per sota, i la profunditat dels forats no sol superar una determinada proporció (obertura).

El forat enterrat fa referència al forat de connexió situat a la capa interior de la placa de circuit imprès, que no s’estén a la superfície del tauler. Els dos tipus de forats anteriors es troben a la capa interior de la placa del circuit, que es completa pel procés de modelat de forat abans de la laminació, i es poden sobreposar diverses capes interiors durant la formació del forat.

El tercer tipus s’anomena forats, que passen per tota la placa de circuit i es poden utilitzar per aconseguir una interconnexió interna o com a forats de posicionament d’instal·lació per a components. Com que el forat a través és més fàcil d’aconseguir en el procés i el cost és menor, la gran majoria de les plaques de circuit impreses l’utilitzen, en lloc dels altres dos a través de forats. Els forats següents, sense instruccions especials, es consideren a través de forats.

Des d’un punt de vista de disseny, A via es compon principalment de dues parts, una és la meitat del forat de la perforació, i l’altra és la zona de la plataforma de soldadura al voltant del forat de la perforació. La mida d’aquestes dues parts determina la mida de via.

Evidentment, en un disseny de PCB d’alta velocitat i d’alta densitat, els dissenyadors sempre volen que el forat sigui el més petit possible, de manera que es pugui deixar més espai de cablejat, a més, més petita és la seva, la seva pròpia capacitat paràsita és més petita, més adequada per a circuits d’alta velocitat.

Tanmateix, la reducció de la mida via també aporta un augment dels costos i la mida del forat no es pot reduir indefinidament, es limita per la perforació i la tecnologia d’electroplicació: com més petit sigui el forat, més temps triga la perforació, més fàcil és desviar -se del centre; Quan la profunditat del forat és superior a 6 vegades el diàmetre del forat, és impossible assegurar -se que la paret del forat es pugui xapar uniformement amb coure.

Per exemple, si el gruix (a través de la profunditat del forat) d’una placa de PCB de 6 capes normal és de 50 milions, el diàmetre mínim de perforació que els fabricants de PCB poden proporcionar en condicions normals només pot arribar a 8 milions. Amb el desenvolupament de la tecnologia de perforació làser, la mida de la perforació també pot ser més petita i petita, i el diàmetre del forat és generalment inferior o igual a 6mils, ens anomenem microoles.

Els microoles s’utilitzen sovint en el disseny d’IDI (estructura d’interconnexió d’alta densitat) i la tecnologia de microholes pot permetre que el forat es perfora directament al coixinet, cosa que millora molt el rendiment del circuit i estalvia l’espai de cablejat. La via apareix com un punt de ruptura de discontinuïtat d’impedància a la línia de transmissió, provocant un reflex del senyal. Generalment, la impedància equivalent del forat és aproximadament un 12% inferior a la línia de transmissió, per exemple, la impedància d’una línia de transmissió de 50 ohms es reduirà en 6 ohms quan passa pel forat (concretament i la mida de la VIA, el gruix de la placa també està relacionat, no una reducció absoluta).

Tanmateix, la reflexió causada per la discontinuïtat de la impedància via és realment molt petita, i el seu coeficient de reflexió només és:

(44-50)/(44 + 50) = 0,06

Els problemes derivats de la VIA es concentren més en els efectes de la capacitança i la inductància parasitària.

Capacitança paràsita i inductància de Via

Hi ha una capacitança perduda paràsita a la via en si mateixa. Si el diàmetre de la zona de resistència a la soldadura de la capa establerta és D2, el diàmetre del coixinet de soldadura és D1, el gruix de la placa PCB és T, i la constant dielèctrica del substrat és ε, la capacitança paràsita del forat a través és aproximadament:

C = 1.41εTD1/(D2-D1)

L’efecte principal de la capacitança parasitària al circuit és allargar el temps d’augment del senyal i reduir la velocitat del circuit.

Per exemple, per a un PCB amb un gruix de 50 milions, si el diàmetre de la coixinet via és de 20 milions (el diàmetre del forat de la perforació és de 10 milions) i el diàmetre de la zona de resistència de soldadura és de 40 milions, i aleshores podem aproximar la capacitat paràsita de la via per la fórmula anterior:

C = 1.41x4.4x0.050x0.020/(0.040-0.020) = 0,31pf

La quantitat de canvi de temps de pujada causada per aquesta part de la capacitança és aproximadament:

T10-90 = 2,2C (Z0/2) = 2.2x0.31x (50/2) = 17.05ps

A partir d’aquests valors es pot veure que, tot i que la utilitat del retard de pujada causada per la capacitança parasitària d’una sola via no és gaire evident, si la VIA s’utilitza diverses vegades a la línia per canviar entre capes, s’utilitzaran múltiples forats i s’hauria de tenir en compte el disseny. En el disseny real, la capacitança paràsita es pot reduir augmentant la distància entre el forat i la zona de coure (anti-PAD) o reduint el diàmetre del coixinet.

En el disseny de circuits digitals d’alta velocitat, el dany causat per la inductància paràsita és sovint superior a la influència de la capacitança paràsita. La seva inductància de sèries paràsites debilitarà la contribució del condensador de bypass i debilitarà l'efectivitat del filtratge de tot el sistema de potència.

Podem utilitzar la fórmula empírica següent per calcular simplement la inductància paràsita d’una aproximació a través del forat:

L = 5.08H [LN (4H/D) +1]

Quan L es refereix a la inductància de via, h és la longitud de via i D és el diàmetre del forat central. Es pot veure a la fórmula que el diàmetre de la VIA té poca influència en la inductància, mentre que la longitud de la VIA té la major influència en la inductància. Encara utilitzant l'exemple anterior, la inductància fora del forat es pot calcular com:

L = 5.08x0.050 [ln (4x0.050/0.010) +1] = 1.015NH

Si el temps d’augment del senyal és d’1NS, la seva mida d’impedància equivalent és:

Xl = πl/t10-90 = 3.19Ω

Aquesta impedància no es pot ignorar en presència de corrent d’alta freqüència mitjançant, en particular, tingueu en compte que el condensador de bypass ha de passar per dos forats quan connecti la capa de potència i la formació, de manera que es multiplicarà la inductància paràsita del forat.

Com utilitzar el via?

Mitjançant l’anàlisi anterior de les característiques paràsites del forat, podem veure que en el disseny del PCB d’alta velocitat, els forats aparentment simples sovint aporten grans efectes negatius al disseny del circuit. Per tal de reduir els efectes adversos causats per l'efecte paràsit del forat, el disseny pot ser en la mesura del possible:

A partir dels dos aspectes de la qualitat del cost i del senyal, trieu una mida raonable de la mida via. Si cal, podeu plantejar -vos utilitzar diferents mides de vias, com per exemple per als forats de subministrament elèctric o de fils de terra, podeu considerar l’ús d’una mida més gran per reduir la impedància i per al cablejat de senyal, podeu utilitzar una VIA més petita. Per descomptat, a mesura que disminueix la mida de la via, el cost corresponent també augmentarà

Les dues fórmules comentades anteriorment es poden concloure que l’ús d’un tauler de PCB més prim és propici per reduir els dos paràmetres paràsits de la via

El cablejat de senyal de la placa PCB no s'ha de canviar en la mesura del possible, és a dir, intenteu no utilitzar vies innecessàries.

Les vies s’han de perforar als pins de l’alimentació i al sòl. Com més curt sigui el plom entre els pins i els vias, millor. Es poden perforar múltiples forats en paral·lel per reduir la inductància equivalent.

Col·loqueu alguns forats a través dels forats del canvi de senyal per proporcionar el bucle més proper al senyal. Fins i tot podeu col·locar uns forats de terra en excés a la placa PCB.

Per a les plaques de PCB d’alta velocitat amb alta densitat, podeu considerar l’ús de micro-forats.