Die VIA is een van die belangrike komponente van Multi-Layer PCB, en die koste van boor is gewoonlik 30% tot 40% van die koste van die PCB-bord. Eenvoudig gestel, elke gat op die PCB kan 'n VIA genoem word.

Die basiese konsep van die VIA:

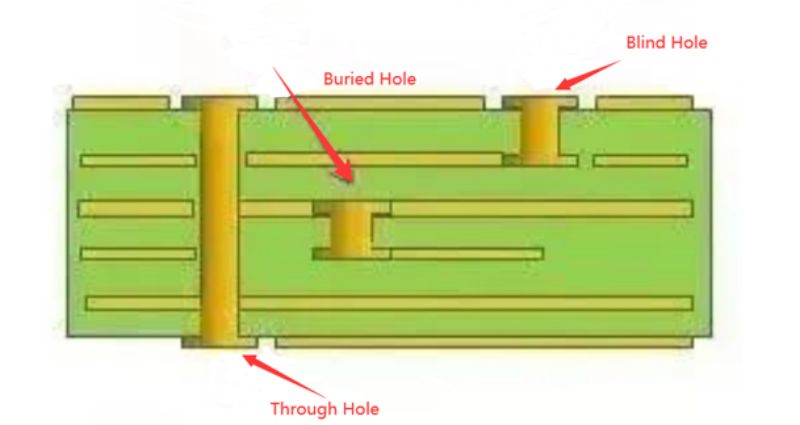

Vanuit die oogpunt van die funksie kan die VIA in twee kategorieë verdeel word: een word gebruik as 'n elektriese verbinding tussen die lae, en die ander word gebruik as 'n bevestiging of posisionering van die toestel. As hierdie gate van die proses af in drie kategorieë verdeel word, naamlik blinde gate, begrawe gate en deur gate.

Blinde gate is op die boonste en onderste oppervlaktes van die gedrukte stroombaanbord geleë en het 'n sekere diepte vir die verbinding van die oppervlakstroombaan en die binneste stroombaan hieronder, en die diepte van die gate oorskry gewoonlik nie 'n sekere verhouding nie (opening).

Die begrawe gat verwys na die verbindingsgat in die binneste laag van die gedrukte kringbord, wat nie tot by die oppervlak van die bord strek nie. Bogenoemde twee soorte gate is in die binneste laag van die kringbord geleë, wat voor laminering deur die gatevormingsproses voltooi is, en verskeie binneste lae kan oorvleuel word tydens die vorming van die gat.

Die derde tipe word deurgate genoem, wat deur die hele kringbord gaan en kan gebruik word om interne interkonneksie te bewerkstellig of as installasie-posisioneringsgate vir komponente. Aangesien die deurgat makliker is om in die proses te bereik en die koste laer is, gebruik die oorgrote meerderheid van die gedrukte kringborde dit, eerder as die ander twee deur gate. Die volgende gate, sonder spesiale instruksies, word deur gate beskou.

Vanuit 'n ontwerp -oogpunt bestaan 'n VIA hoofsaaklik uit twee dele, die een is die middel van die boorgat, en die ander is die sweisplaat rondom die boorgat. Die grootte van hierdie twee dele bepaal die grootte van VIA.

Dit is duidelik dat die ontwerpers in 'n hoë snelheid, hoë-digtheid PCB-ontwerp, altyd die gat so klein as moontlik wil hê, sodat meer bedradingsruimte gelaat kan word, hoe kleiner die Via, sy eie parasitiese kapasitansie is kleiner, meer geskik vir hoëspoed-stroombane.

Die vermindering van die Via -grootte bring egter ook 'n toename in koste, en die grootte van die gat kan nie onbepaald verminder word nie, dit word beperk deur boor- en elektroplatietegnologie: hoe kleiner die gat, hoe langer neem die boor, hoe makliker is dit om van die sentrum af te wyk; As die diepte van die gat meer as 6 keer die deursnee van die gat is, is dit onmoontlik om te verseker dat die gatwand eenvormig met koper bedek kan word.

Byvoorbeeld, as die dikte (deur die gatdiepte) van 'n normale 6-laag PCB-bord 50mil is, kan die minimum boordiameter wat PCB-vervaardigers onder normale omstandighede kan voorsien, slegs 8 miljoen bereik. Met die ontwikkeling van laserboor -tegnologie, kan die grootte van die boor ook kleiner en kleiner wees, en die deursnee van die gat is oor die algemeen minder as of gelyk aan 6 miljoen, word ons mikro -gate genoem.

Mikro -gate word dikwels gebruik in HDI (hoë -digtheid interkonnekstruktuur) -ontwerp, en mikrobattegnologie kan die gat direk op die pad geboor word, wat die kringprestasie aansienlik verbeter en die bedradingruimte bespaar. Die VIA verskyn as 'n breekpunt van impedansie -diskontinuïteit op die transmissielyn, wat die sein weerspieël. Oor die algemeen is die ekwivalente impedansie van die gat ongeveer 12% laer as die transmissielyn, byvoorbeeld, sal die impedansie van 'n transmissielyn van 50 ohm met 6 ohm verminder word as dit deur die gat gaan (spesifiek en die grootte van die VIA, die plaatdikte is ook verwant, nie 'n absolute vermindering nie).

Die refleksie wat veroorsaak word deur die impedansie -diskontinuïteit via is egter baie klein, en die refleksiekoëffisiënt is egter slegs:

(44-50)/(44 + 50) = 0,06

Die probleme wat voortspruit uit die VIA, is meer gekonsentreer op die gevolge van parasitiese kapasitansie en induktansie.

Via se parasitiese kapasitansie en induktansie

Daar is 'n parasitiese verdwaalde kapasitansie in die via self. As die deursnee van die soldeersweerstandsone op die gelê laag D2 is, is die deursnee van die soldeerkussing D1, die dikte van die PCB -bord is T, en die diëlektriese konstante van die substraat is ε, is die parasitiese kapasitansie van die deurgat ongeveer:

C = 1.41εtd1/(d2-d1)

Die belangrikste effek van die parasitiese kapasitansie op die stroombaan is om die stygingstyd van die sein te verleng en die snelheid van die stroombaan te verminder.

Byvoorbeeld, vir 'n PCB met 'n dikte van 50 miljoen, as die deursnee van die Via -kussing 20 miljoen is (die deursnee van die boorgat is 10 miljoen) en die deursnee van die soldeersweerstandsone 40 miljoen, dan kan ons die parasitiese kapasitansie van die VIA deur die bogenoemde formule benader:

C = 1.41x4.4x0.050x0.020/(0.040-0.020) = 0.31pf

Die hoeveelheid stygingstydverandering wat deur hierdie deel van die kapasitansie veroorsaak word, is grofweg:

T10-90 = 2.2C (Z0/2) = 2.2x0.31x (50/2) = 17.05ps

Uit hierdie waardes kan gesien word dat hoewel die nut van die stygingvertraging wat veroorsaak word deur die parasitiese kapasitansie van 'n enkele Via nie baie voor die hand liggend is nie, as die VIA 'n paar keer in die lyn gebruik word om tussen lae te skakel, verskeie gate gebruik sal word, en die ontwerp noukeurig oorweeg moet word. In die werklike ontwerp kan die parasitiese kapasitansie verminder word deur die afstand tussen die gat en die koperarea (anti-pad) te verhoog of die deursnee van die kussing te verminder.

In die ontwerp van hoë-snelheid digitale stroombane is die skade wat deur die parasitiese induktansie veroorsaak word, dikwels groter as die invloed van die parasitiese kapasitansie. Die parasitiese reeks induktansie sal die bydrae van die omseilkondensator verswak en die filtereffektiwiteit van die hele kragstelsel verswak.

Ons kan die volgende empiriese formule gebruik om eenvoudig die parasitiese induktansie van 'n deurgatbenadering te bereken:

L = 5.08H [LN (4H/D) +1]

Waar L verwys na die induktansie van Via, is H die lengte van Via, en D is die deursnee van die sentrale gat. Uit die formule kan gesien word dat die deursnee van die Via min invloed op die induktansie het, terwyl die lengte van die VIA die grootste invloed op die induktansie het. Gebruik nog bogenoemde voorbeeld, kan die buite-gate-induktansie bereken word as:

L = 5.08x0.050 [Ln (4x0.050/0.010) +1] = 1.015NH

As die stygingstyd van die sein 1ns is, dan is die ekwivalente impedansiegrootte:

Xl = πl/t10-90 = 3.19Ω

Sodanige impedansie kan nie geïgnoreer word in die teenwoordigheid van hoëfrekwensiestroom deur veral daarop te let dat die omseilkondensator deur twee gate moet gaan wanneer die kraglaag en die vorming verbind word nie, sodat die parasitiese induktansie van die gat vermenigvuldig sal word.

Hoe om die VIA te gebruik?

Deur bogenoemde ontleding van die parasitiese eienskappe van die gat, kan ons sien dat in 'n hoë snelheid PCB-ontwerp, oënskynlik eenvoudige gate dikwels 'n groot negatiewe gevolge vir die ontwerp van die kring het. Om die nadelige gevolge wat veroorsaak word deur die parasitiese effek van die gat te verminder, kan die ontwerp sover moontlik wees:

Kies 'n redelike grootte van die VIA -grootte van die twee aspekte van koste en seingehalte. As dit nodig is, kan u dit oorweeg om verskillende groottes van VIA's te gebruik, soos vir kragbron- of gronddraadgate, kan u dit oorweeg om 'n groter grootte te gebruik om die impedansie te verminder, en vir seinbedrading kan u 'n kleiner VIA gebruik. Namate die grootte van die VIA -daal, sal die ooreenstemmende koste natuurlik ook styg

Die twee formules wat hierbo bespreek is, kan tot die gevolgtrekking gekom word dat die gebruik van 'n dunner PCB -bord bevorderlik is vir die vermindering van die twee parasitiese parameters van die VIA

Die seinbedrading op die PCB -bord moet nie sover moontlik verander word nie, dit wil sê, probeer om nie onnodige VIA's te gebruik nie.

Vias moet in die penne van die kragbron en die grond geboor word. Hoe korter die voorsprong tussen die penne en die VIA's, hoe beter. Verskeie gate kan parallel geboor word om die ekwivalente induktansie te verminder.

Plaas sommige gegrondde deurgate naby die deurgate van die seinverandering om die naaste lus vir die sein te gee. U kan selfs 'n paar oortollige grondgate op die PCB -bord plaas.

Vir hoëspoed-PCB-planke met 'n hoë digtheid, kan u dit oorweeg om mikro-gate te gebruik.